# Proceedings of the

# $\mathbf{8}^{th}$ Junior Researcher Workshop on Real-Time Computing

# **JRWRTC 2014**

http://www.cister.isep.ipp.pt/jrwrtc2014/

Versailles, France October 8-10, 2014

## **Message from the Workshop Chairs**

We are delighted to welcome you to the  $8^{th}$  Junior Researcher Workshop on Real-Time Computing taking place in Versailles, October 2014. As part of the  $22^{nd}$  International Conference on Real-Time and Network Systems (RTNS), the workshop provides junior researchers the opportunity to present their work, share and discuss their ideas and meet with the real-time community in a relaxed forum.

We would like to take this opportunity to express our gratitude to the members of the Program Committee listed below for thoroughly reviewing all the submitted papers. We would also like to thank all the authors who submitted their work to the workshop and hence contributed to its success. This year, JRWRTC accepted 13 of 15 peer-reviewed papers, which cover various topics of the real-time field such as scheduling, WCET analysis, time predictability, mixed criticality and sensor networks.

Yet, JRWRTC would not have been possible without the support of many people. We especially thank the General Chairs Mathieu Jan (CEA LIST, Gif-sur-Yvette, France) and Belgacem Ben Hedia (CEA LIST, Gif-sur-Yvette, France) and the local organizing committee, as well as the Program Chairs Joël Goossens (Université Libre de Bruxelles (ULB), Belgium) and Claire Maiza (Grenoble INP / Verimag, France) of RTNS 2014, for their help and support and for allowing this workshop to be, once more, part of the main event of the conference.

On behalf of the Program Committee, we wish you a pleasant workshop. We hope you will enjoy the presentations and invite you to discuss the presented ideas with the authors during the poster session.

Dorin Maxim, Polytechnic Institute of Porto Geoffrey Nelissen, Polytechnic Institute of Porto JRWRTC 2014 Workshop Chairs

## **Program Committee**

Bader Alahmad The University of British Columbia, Canada

Andrea Baldovin Università degli Studi di Padova, Italy

Hugo Cruz-Sanchez MyFOX, France

Pontus Ekberg Uppsala University, Sweden

Glenn Elliott University of North Carolina, USA

Vikram Gupta Polytechnic Institute of Porto, Portugal

Junsung Kim Carnegie Mellon University, USA

Leonidas Kosmidis Barcelona Supercomputing Center, Spain

Vincent Legout Virginia Tech, USA

Mitra Nasri TU Kaiserslautern, Germany

Moritz Neukirchner TU Braunschweig, Germany

Victor Pollex Ulm University, Germany

Manar Qamhieh Université Paris-Est, France

Abhilash Thekkilakattil Mälardalen University, Sweden

Martijn Van Den Heuvel TU Eindhoven, The Netherlands

# **Table of Contents**

| Message from the Workshop Chairs                                                                                                                 | iii |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Framework for the Optimization of the WCET of Programs on Multi-Core Processors <i>Maximilian John and Michael Jacobs</i>                      | 1   |

| Statically Resolving Computed Calls via DWARF Debug Information                                                                                  | 5   |

| Schedulability-Oriented WCET-Optimization of Hard Real-Time Multitasking Systems                                                                 | 9   |

| Accounting for Cache Related Pre-emption Delays in Hierarchical Scheduling with Local EDF Scheduler                                              | 13  |

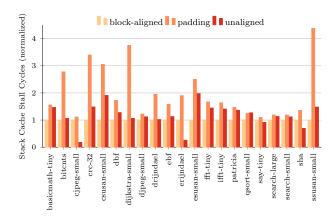

| Alignment of Memory Transfers of a Time-Predictable Stack Cache                                                                                  | 17  |

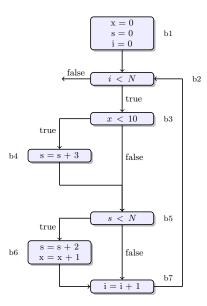

| The WCET Analysis using Counters - A Preliminary Assessment                                                                                      | 21  |

| Adaptation of RUN to Mixed-Criticality Systems                                                                                                   | 25  |

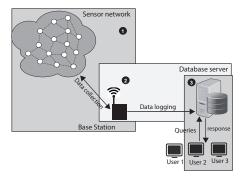

| Study of Temporal Constraints for Data Management in Wireless Sensor Networks                                                                    | 29  |

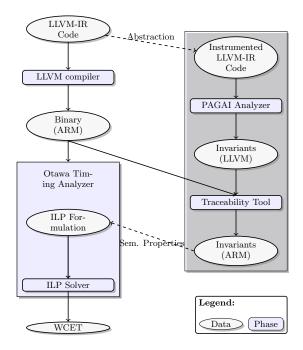

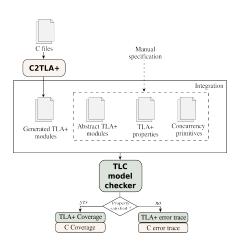

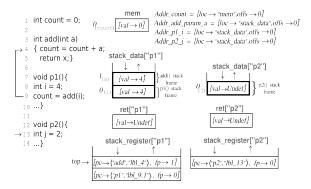

| An Approach for Verifying Concurrent C Programs                                                                                                  | 33  |

| Resource Sharing Under a Server-based Semi-partitioned Scheduling Approach                                                                       | 37  |

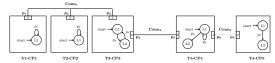

| Externalisation of Time-Triggered communication system in BIP high level models                                                                  | 41  |

| Towards Exploiting Limited Preemptive Scheduling for Partitioned Multicore Systems  Abhilash Thekkilakattil, Radu Dobrin and Sasikumar Punnekkat | 45  |

| Multi-Criteria Optimization of Hard Real-Time Systems                                                                                            | 49  |

## A Framework for the Optimization of the WCET of Programs on Multi-Core Processors

Maximilian John Saarland University Saarbrücken, Germany s9mnjohn@stud.uni-sb.de Michael Jacobs Saarland University Saarbrücken, Germany jacobs@cs.uni-sb.de

## **ABSTRACT**

For a timing-critical system, it is mandatory to guarantee upper bounds on the execution times of its programs. Such bounds can be derived using worst-case execution time (WCET) analysis. WCET analysis for multi-core processors is challenging as the behavior of one processor core in general depends on the behavior of the other cores. A common option to reduce this dependency is the use of time division multiple access (TDMA) bus arbitration.

We consider a multi-core processor with a shared TDMA bus. A system schedule for this processor assigns hard real-time tasks to processor cores and determines their execution order. A bus schedule determines which processor core is allowed to access the bus at which points in time. The WCET of a program executed on the processor depends on the choice of the system schedule and the bus schedule. We propose a framework that aims at reducing the overall WCET of the system by simultaneously constructing both schedules. Furthermore, we introduce a system model that allows to describe the considered programs in a simple way. We subsequently discuss how to overcome some restrictions of our system model. Finally, we sketch possible evaluations of our framework.

## 1. INTRODUCTION

For timing-critical applications, it is mandatory that their response times do not exceed the deadlines defined by the physical environment. A timing-critical application may be implemented by a composition of several programs. If there is a safe estimation of the WCET of each such program, we can give an upper bound on the total response time of the application. In many cases, it is important that these estimates are relatively tight in order to verify the timeliness of the application. WCET analysis is commonly used to derive an upper bound on the execution times of a program and thereby estimates the WCET of the program. The WCET analysis of programs executed on single-core processors is already studied well [1].

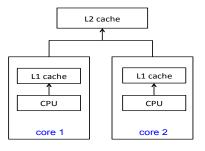

Multi-core processors typically share resources—like caches or buses—between several processor cores. Some of the advantages of multi-core processors are reduced weight, reduced production costs and a good ratio between performance and energy consumption. Therefore, it is a current trend to also use them for the design of timing-critical embedded systems. However, the resource sharing leads to the cores behaving in a different manner than with dedicated resources of the same capacities. We refer to these effects as *shared resource interference* [2]. As a consequence of this interference, the

behavior of one processor core may depend on the behavior of all other processor cores. In this case, a precise WCET analysis is challenging. It is no longer sufficient to focus on one core's behavior in order to derive a tight upper bound on the execution times of a program executed on it. To bound the complexity of such an analysis, existing approaches mainly concentrate on bounding the direct timing penalties due to shared resource interference, e.g. the time that a processor core is blocked at the shared bus before its access request is granted [3, 4].

In this paper, we focus on the interference caused by shared buses. It is common to assume that the shared bus must not be accessed by more than one processor core at the same time. Therefore, there is typically an instance defining which core is allowed to access the shared bus at a particular point in time—the bus arbiter. We say that a processor core is blocked as long as one of its access requests is not granted by the arbiter. Obviously, the blocking time contributes to the overall execution time of a processor while executing a particular program. Thus, it is important to also consider the bus blocking in WCET analysis. In general, the precise consideration of the bus blocking experienced by one core requires the examination of the concurrent cores. This makes WCET analysis complex. However, in combination with TDMA bus arbitration, the bus blocking that one processor core suffers from does not depend on concurrent cores. This allows the WCET analysis to precisely model bus blocking without modeling concurrent processor cores. In this paper, we assume a system with a shared bus arbitrated according to a TDMA policy.

TDMA bus arbitration bases its decisions on a static bus schedule that assigns every time slot to the processor core which is allowed to access the bus at that instant. A program's execution time heavily depends on the static choice of this bus schedule. Thus, the eased analyzability comes at the cost of having to choose a bus schedule. This choice of the bus schedule should ideally lead to low WCET bounds for time-critical programs.

We present a heuristical framework that optimizes the system schedule and the bus schedule for a given task set and a given number of processor cores. The optimization goal is to minimize the WCET. The framework is modular in the sense of defining an interface for heuristics that select the task to be executed next on a particular processor core.

Throughout our paper, we make the following contributions:

1. A simple system model for hard real-time tasks with access to a shared bus

- 2. A modular framework for the optimization of the WCET of hard real-time systems

- 3. Approaches to apply the framework to real-world systems

#### 2. SYSTEM MODEL

Our model is denoted by the following characteristic parameters. It consists of several equal processor cores, a shared bus and a set of hard real-time tasks. Each task may request access to the shared bus at several points in time during its execution. Assume for the moment that every access request to the bus is granted immediately. Figure 1 depicts an exemplary task. It has two bus accesses (marked purple) at time units 1 and 3, respectively. The second access is twice as long as the first one. The execution time of this task—assuming that both access requests are granted immediately—is 6 time units. Note that it is a fundamental assumption of our system model that every task is characterized by a single execution behavior and thus also by a single execution time (we will sketch in Section 4.2.1 how to support tasks with several execution behaviors).

Figure 1: An example task

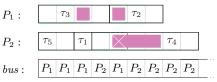

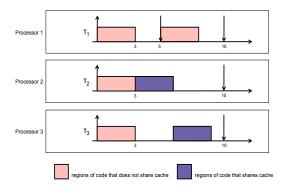

In our model all tasks are released simultaneously at time unit 0 and have to be executed exactly once. We assume that a task can be started independently of the progress of other tasks. In addition, there is a static assignment from tasks to the processor cores. The tasks assigned to a particular processor core are scheduled non-preemptively following a static task order. The use of non-preemptive scheduling offers several advantages for hard real-time systems [5]. We refer to the combination of the task assignment and the task orders as system schedule. Figure 2 shows an example of a system schedule.

Figure 2: A system schedule

The example system schedule assigns five tasks to two processor cores. Tasks  $\tau_2$  and  $\tau_3$  are executed on the first processor core whereas the remaining tasks are executed on the second one. Furthermore, the presented system schedule describes the task order per core, e.g. task  $\tau_2$  is executed after task  $\tau_3$ . According to this system schedule, both processor cores request access to the bus at time unit 4. However, the shared bus can only serve one processor core per time unit. In the following, we introduce a bus arbitration to guarantee this.

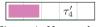

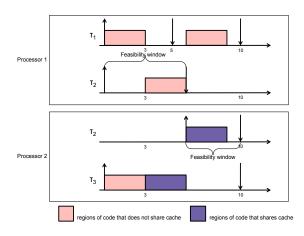

Our system model uses TDMA bus arbitration. That means, the arbiter has static knowledge about which processor core is allowed to access the bus at which point in time. This static knowledge is present in the form of a bus schedule which maps time units to processor cores. Note that we do not rely on periodic bus schedules. An access request of a core that is not allowed to access the bus is blocked. Figure 3 shows the system schedule of Figure 2 supplemented with a bus schedule.

Figure 3: The effect of a bus schedule

Note that processor core  $P_2$  is blocked at time unit 4 because  $P_1$  is allowed to access the bus. Thus, the considered pair of system schedule and bus schedule leads to a response time of 9 time units for task  $\tau_4$ . As a consequence, the overall execution time (maximum over the response times of all tasks) also amounts to 9 time units.

Intuitively, we assume that the number of time units that a task is blocked just adds up to its execution time. This assumption is commonly known as *timing compositionality*. For a detailed discussion of timing compositionality we refer to an article by Hahn et al. [6].

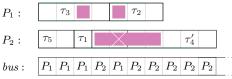

For the next example, consider the same system schedule and bus schedule as in Figure 3. But this time, we replace  $\tau_4$  by  $\tau_4'$ .

Figure 4: New task  $\tau'_4$

This leads to the access of task  $\tau_4'$  being interrupted. According to our system model, interrupted bus accesses have to be restarted from scratch. Therefore, the system schedule and the bus schedule lead to an overall execution time of 10 time units for the task set (as shown in Figure 5). Thus, the number of time units used for interrupted accesses also adds up to the execution time in a compositional way.

Figure 5: An interrupted and restarted access

**Problem statement:** Obviously, the system schedule as well as the bus schedule influence the overall execution time of the system. We assume that the task set and the number of processor cores is already given. Based on this input, we try to find a pair of system schedule and bus schedule leading to a short overall execution time for the task set.

As our system model assumes a single execution time per task (ignoring possible bus blocking effects), the overall execution time of the task set and the overall WCET of the task set coincide for our system model. For the sake of generality and comparability, we will only use the term overall WCET in the rest of this paper.

Finding an optimal static multiprocessor schedule is known to be a hard optimization problem already in the absence of accesses to a shared bus [7]. Therefore, we focus on developing a heuristic approach that finds a pair of system schedule and bus schedule leading to an overall WCET close to the possible minimum.

## 3. APPROACH

In this section, we present a framework that allows us to heuristically optimize the overall WCET of a task set on a

```

Data: tasks: set of tasks,

n: number of processor cores,

th: task selection heuristic,

bh: bus schedule heuristic

1 (sys, bus) \leftarrow empty schedules for n processor cores;

2 while tasks \neq \emptyset do

task \leftarrow th(tasks, sys, bus);

p\_idle \leftarrow \text{find first idle core in } (sys, bus);

sys \leftarrow add \ task \ in \ sys \ to \ p\_idle;

5

bus \leftarrow bh(sys, bus, "partial");

6

tasks \leftarrow tasks \setminus \{task\};

s end

\mathbf{9} \ bus \leftarrow bh(sys, bus, "complete");

10 return (sys, bus);

```

Algorithm 1: Optimization procedure

multi-core processor system by choosing a system schedule and a bus schedule. It is centered around Algorithm 1, which is similar to the approach by Rosén et al. [8]. In contrast to the work of Rosén, however, our algorithm is parametric in the task selection heuristic. It integrates the construction of the system schedule and the construction of the bus schedule by alternately adding a task to the system schedule and building a part of the bus schedule.

The algorithm takes as input parameters the set of tasks, the number of processor cores, the task selection heuristic th and the bus schedule heuristic bh. The task selection heuristic th selects one of the remaining tasks to be added to the already existing system schedule. It may base its decision on the already constructed parts of the system schedule and the bus schedule. The bus schedule heuristic bh continues the construction of the given bus schedule.

Algorithm 1 starts by assuming that none of the processor cores is assigned any of the tasks. We call this an empty system schedule. Analogously, an empty bus schedule is vet undefined for all time slots. In line 3 we select one of the remaining tasks to be added to the system schedule. As a next step, we consider the first point in time for which the bus schedule is yet undefined. Now, let  $p_{-idle}$  be one of the processor cores which has finished the execution of its assigned tasks up to this point. Line 5 extends the existing system schedule by assigning the selected task to  $p_{-}idle$ . The task order of the system schedule is extended such that the added task is executed after the tasks previously assigned to  $p_{-idle}$ . After this extension, there may be points in time for which the bus schedule is not yet defined although no processor core is idle. Therefore, line 6 continues the construction of the bus schedule until one of the processor cores is idle again ("partial"). Afterwards, we remove the selected task from the set of remaining tasks (line 7) and repeat the previous lines until no task remains (line 2). As a final step, line 9 continues the construction of the bus schedule up to the point in time at which all processor cores are idle ("complete").

## 4. FUTURE WORK

## 4.1 Access-Aware Task Selection Heuristics

The quality of the results obtained by our framework is mainly determined by the quality of the heuristics used for the construction of the system schedule and the bus schedule.

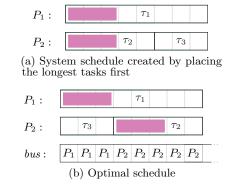

Figure 6: Influence of the system schedule on the possible execution time

Figure 7: Computing a single execution behavior

Thus, it will be our main goal to develop and compare different heuristics.

A recent approach by Rosén et al. [8] presents a rather simple task selection heuristic which can be used in our framework. In combination with our system model, this heuristic boils down to selecting the longest remaining task to be scheduled next. An exemplary system schedule created according to this heuristic is depicted in Figure 6(a). Note that any bus schedule added to this system schedule leads to a blocking of at least 3 time units for at least one of the processor cores.

In contrast, Figure 6(b) shows that it is in fact possible to come up with a system schedule that fully utilizes all processor cores without necessarily delaying one of them. Intuitively, this is possible because the system schedule arranges the tasks in a way that no bus accesses overlap. This motivates us to develop task selection heuristics which try to reduce the access overlaps. In order to do so, it is mandatory to take into account the access behavior of the different candidate tasks.

## 4.2 Generalizing the Approach

#### 4.2.1 Tasks with Multiple Execution behaviors

Figure 8: Bus schedule with bus-processor ratio 4

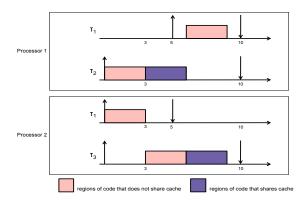

Our system model assumes tasks with a single execution behavior (ignoring possible bus blocking effects). This assumption guarantees the efficiency of our approach as there is no need to enumerate many different execution behaviors per task.

However, real-world tasks executed on modern hardware platforms typically exhibit various execution behaviors. We aim at supporting such tasks without giving up the efficiency and simplicity of our system model. In order to support a task with a set of execution behaviors, we propose to replace this set by a single execution behavior. For every possible bus schedule, this single execution behavior should lead to an execution time at least as high as the maximum over the execution times of all members of the original set.

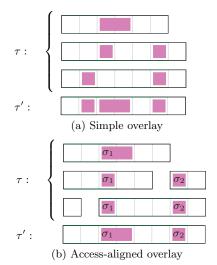

One possible way to obtain the single execution behavior is to overlay the execution behaviors of the original set. The principle of overlaying is depicted in Figure 7(a). Essentially, every relative position of the resulting behavior is marked as access if at least one of the original behaviors has an access at this position. Note that the resulting behavior may contain strictly more time units of bus accesses than every original behavior.

Another approach to the construction of the single execution behavior aligns the accesses of the original behaviors before performing the overlay. Figure 7(b) illustrates this approach for the same set of behaviors as already used in the example of Figure 7(a). The intuition is that we number the accesses in the increasing order of their appearance per execution behavior. Subsequently, we add the minimal amount of margin to the execution behaviors such that all accesses with the same number start at the same instant. We see that the resulting execution behavior contains one time unit of bus access less than the result in Figure 7(a). However, this comes at the cost of a longer execution time (8 time units compared to 7 in Figure 7(a)).

## 4.2.2 Task Dependencies

So far, we consider a scenario without task dependencies. However, supporting such dependencies in our approach is straight-forward. The task selection heuristic simply has to return a task for which all predecessors in the dependency graph already finished their execution.

This treatment of the task dependencies may—in certain situations—lead to the task selection heuristic not being able to select any of the remaining tasks. We can simply solve this problem by allowing the heuristic to return a dummy task of length 1 without bus access in such cases.

## 4.2.3 Less Fine-Grained Bus Schedules

In our system model, we assume that we can define the bus schedule at the same granularity of time units as the execution behavior of the tasks. If we assume that our tasks are defined at the granularity of a processor cycle, then for many realistic hardware platforms the bus schedule will not be definable at the same granularity. It is common to have an integer factor K defining the bus-processor ratio for a given hardware platform. Then the value of the bus schedule may only change at integer multiples of K.

$$\forall n \in \mathbb{N}. \ n \not\equiv 0 \mod K \Rightarrow bus(n) = bus(n-1)$$

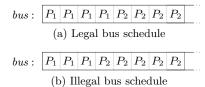

Consider for example a bus-processor ratio of 4. Figure 8(a) shows a bus schedule that conforms to this ratio. The bus schedule in Figure 8(b) does not conform to this as it changes its value at time unit 3.

Our approach naturally supports such restrictions by using bus schedule heuristics that only create allowed bus schedules.

#### 4.3 Evaluation

We plan to extract execution behaviors (as defined by our system model) from real-world programs. Subsequently, we intend to construct task sets based on these behaviors. We will use these task sets to compare the effectiveness and efficiency of different task selection and bus schedule heuristics. Additionally, we will compare the different heuristics to provably optimal results for relatively small examples.

Furthermore, we are interested in how the different ways to generalize our approach (cf. Section 4.2) influence the overall WCET obtained by our approach. For example, we want to find out which is the best way to replace a set of execution behaviors by a single behavior.

## 5. REFERENCES

- R. Wilhelm et al., "The worst-case execution-time problem — overview of methods and survey of tools," ACM Transactions on Embedded Computing Systems, vol. 7, no. 3, pp. 36:1–36:53, 2008.

- [2] A. Abel et al., "Impact of resource sharing on performance and performance prediction: A survey," in CONCUR, 2013, pp. 25–43.

- [3] R. Pellizzoni and M. Caccamo, "Impact of peripheral-processor interference on weet analysis of real-time embedded systems," *IEEE Transactions on Computers*, vol. 59, pp. 400–415, 2010.

- [4] R. Pellizzoni et al., "Worst case delay analysis for memory interference in multicore systems," in Proceedings of the Conference on Design, Automation and Test in Europe, 2010, pp. 741–746.

- [5] M. Marouf and Y. Sorel, "Scheduling non-preemptive hard real-time tasks with strict periods," in *Emerging Technologies Factory Automation (ETFA)*, 2011 IEEE 16th Conference on, 2011, pp. 1–8.

- [6] S. Hahn et al., "Towards compositionality in execution time analysis – definition and challenges," in Proceedings of the International Workshop on Compositional Theory and Technology for Real-Time Embedded Systems, 2013.

- [7] M. R. Garey and D. S. Johnson, Computers and Intractability: A Guide to the Theory of NP-Completeness, 1990.

- [8] J. Rosén et al., "Bus access optimization for predictable implementation of real-time applications on multiprocessor systems-on-chip," in Proceedings of the 28th IEEE International Real-Time Systems Symposium, 2007, pp. 49-60.

# Statically Resolving Computed Calls via DWARF Debug Information

Florian Haupenthal

AbsInt Angewandte Informatik GmbH

Science Park 1

66123 Saarbrücken, Germany

haupenthal@absint.com

## **ABSTRACT**

Allowing virtual functions for safety-critical (embedded) systems allows for easier programming, but makes static program analysis harder. Classical analyses are too imprecise or too expensive to resolve computed calls introduced by virtual functions in C++. We present an approach that uses the DWARF debug information as an additional information source to resolve computed calls. We evaluate our approach on a set of example programs on which a value analysis cannot resolve all computed calls. Our approach resolves all the computed calls without increasing the cost of the value analysis, but still needs to be tested on real-world programs.

## **Categories and Subject Descriptors**

D.1.5 [Software Engineering]: Object-oriented Programming; D.2.4 [Software Engineering]: Software/Program Verification; D.3.2 [Software Engineering]: C++; D.4.7 [Software Engineering]: Real-time systems and embedded systems

## **General Terms**

Verification

## **Keywords**

Computed calls, static program analysis, DWARF debug information  $\,$

## 1. INTRODUCTION

Safety-critical (embedded) software ideally runs through a verification process. This process aims to provide guarantees for every possible execution. The behaviour of a single execution depends on the program, the state of the underlying hardware, and the environment – input or sensor values for example. These configurations can be unknown. A verification by running the program for every possible configuration separately is expensive or infeasible. An abstract interpretation in the form of a static program analysis considers all possible configurations in one analysis run.

One example is a stack analysis. An embedded system provides a limited amount of memory and a program must stay within this limit. Therefore, an analysis has to provide an upper bound on the maximum amount of memory used by a program. A part of this amount is the needed space for local variables. The compiler introduces additional memory use. For example, if one function calls another one, the compiler introduces code that stores the address where the

execution of the program has to proceed when the called function returns. A stack frame for each function instance contains this information. For each function call, the program creates an additional stack frame and puts it on top of the stack. If a function returns, its frame gets removed from the stack. Therefore, an analysis has to find the maximum height of the stack.

For some function calls, the call target or whether a concrete call actually takes place depends on run-time information. A stack analysis needs to account for every call target that is possible in at least one execution.

```

int main(int argc, char** argv)

{

foo();

if(argc != 23) {

bar();

}

return 0;

}

```

Figure 1: Excerpt of an example program with two function calls and a maximum of two stack frames on the stack at once. Whether the second call takes place depends on run-time information.

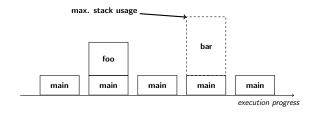

Figure 2: Different stack heights during an execution of the program from Figure 1.

Figure 1 shows an excerpt of an example program with two function calls. The first call happens in every execution. Whether the second call takes place, depends on the input values. For our static analysis, we have to consider the highest possible stack. This is the one for an execution where the second call actually takes place.

Figure 3: Static call graph of the example program from Figure 1.

Figure 2 shows a graphical representations of the stacks. 9 The size of each box represents the size of the stack frame. 10 The dashed lines indicate that the corresponding frame will only be there in some executions. For a guarantee over all possible executions, we have to consider this call.

Figure 3 shows a static call graph for this program. It is static as it shows a call edge for the second function call. The  $a^3$  tool from AbsInt uses binaries as inputs and transforms them into a graph representation. Besides the stack usage analysis, the value analysis and the worst-case execution time analysis use this representation as well. Note that we use this graph representation without the source code.

Virtual functions as part of C++ can lead to calls with more than one call target. The compiler automatically resolves calls with only one possible target. If there are more possible targets, the compiler introduces a computed call. This is a call, where the program can look up which function to call at run time.

C++ programs generate objects from class descriptions. Every class description is a type. Objects start with a pointer to their corresponding class description. This class description starts with a list of pointers to the functions that this class implements itself or that this class has available because it inherits it from another class. We call this list a vtable.

The example in Figure 4 shows three code snippets. All of them show virtual function calls. The compiler can resolve the first one. Only one call target is possible and therefore, there is a concrete address for the function call. For the remaining ones, it will produce computed calls.

For the second example, a precise value analysis can still track the possible targets after the condition. Using the results of this analysis, we can create a call graph, containing two edges for the two different possible call targets. The value analysis has to keep a separate value for each possible dynamic type. This increases the cost of the whole value analysis.

For the third example, the precision in the value analysis is useless. We analyse only a part of a program. The only information for the first call is the static type. However, the binary contains no types. A value analysis can track the pointer after the assignment in line 4, but after the store in line 6 it loses every information, since this is a store to an unknown memory location.

An analysis using static type information can resolve all computed calls from the example above to generate the call graph. Since compilers can optimise their output, it is hard to interconnect points in the resulting binary and the source code. Therefore, it is hard to transfer the static type information from the source code to the call in the binary.

DWARF is a standardised format allowing a debugger to read additional information for the current state of the execution of an executable. This debug information contains the

```

1 C c;

2 c.cookie();

```

```

1 A* a;

2 B b;

3 C c;

4

5 if(????)

6 a = &b;

7 else

8 a = &c;

9

10 a->cookie();

```

Figure 4: Code snippets with virtual functions of different analysability. The classes B and C in these snippets extend A and have own implementations for cookie(). Note that the store in line 6 is a store to an unknown memory location.

static types of variables and a relation between registers on the binary level and variables in the source code. Combining all this information, we can find a safe (over-)approximation for the set of possible call targets.

An advantage of reading the DWARF debug information is that it is similar for different compilers and platforms. This reduces the platform dependent parts of our code to a minimum.

#### 1.1 Contributions

We introduce an extension to the current analysis framework of the  ${\bf a}^3$  tool by AbsInt. This extension makes the DWARF debug information available to analyses. We use this additional information to resolve former unresolved computed calls originating from virtual function calls. With this extension, we can analyse programs that were only analysable when manually annotated.

These are our contributions in short:

- We implemented a static reader for DWARF debug information in the a<sup>3</sup> tool by AbsInt. A debugger interprets this information while running an instance of the program. Our implementation can extract information without having a running instance.

- We used the additional information to analyse computed calls originating from virtual function calls for PowerPC.

- Computed calls originating from virtual functions were not automatically analysable. Therefore, programmers omitted using them and example binaries are hard to

find. We evaluated our approach with artificial examples. This shows at least that an automatic analysis of these calls is possible.

## 2. OUR APPROACH

Our approach consists of two parts. We implemented a static reader for DWARF debug information and scanned the binary for patterns of computed calls.

The DWARF format uses compression. When a debugger uses the DWARF debug information, it has a running instance of a program. It is only interested in information about the current state of execution of the program. The DWARF format takes advantage of these restrictions. A debugger can resolve relative addresses during debugging.

Even the incomplete, relative information can be useful. A debugger can jump from one type description to its base type description, starting from the current **this** pointer. Without a running instance of the program, our implementation can only store all the descriptions and their relations. This suffices to reconstruct the complete type hierarchy, but is separated from a concrete object. A debugger needs to know how to interpret the value of a local variable for a certain state of execution. Therefore, the DWARF debug information can contain a frame base relative location of this variable. The debugger knows the current state of execution and can resolve this location. Our interest is only in the type of the variable, but not the value. Therefore, it suffices to relate the offsets of the load instructions in the binary to these relative locations.

We store all read DWARF debug information into a sqlite database.

```

1

lwz

r9 , +0 (r9)

2

addi

r9, r9, +4

r0, +0(r9)

3

lwz

4

mtspr

{\rm ctr}\;,\;\; {\rm r0}

5

lwz

r3 + 8(r31)

6

bctrl

```

Figure 5: Typical assembler sequence for a computed call on a PowerPC.

Figure 5 shows how a typical instruction sequence for a computed call on a PowerPC looks like. The first instruction loads the address of the vtable. The second instruction adds an offset to this address to load the second entry of the vtable. The address of the second entry is the address of the first one plus the size of one pointer, 4 bytes. The third instruction loads the address of the call target from the vtable. Instead of adding an offset to the address of the vtable, optimised code loads with an offset immediately. This platform uses a special purpose register for this function call. The fourth instruction loads the target address into this special purpose register. The fifth instruction copies the **this** pointer. In optimised code, this only happens if the called function uses the **this** pointer. The last instruction is the actual call to the target.

We implemented a pattern, matching this sequence and its variations. Our approach wants to use the static type of the variable via that the virtual function is called. The assembler only shows registers. If there is a load for copying the **this** pointer (line 5), our approach can use the source register

from this instruction. If an optimisation removed this load, it can use the load of the vtable address (line 1). We use this order since the pattern matching starts at the unresolved call in the last line and goes backwards. The DWARF debug information contains information on which variable is assigned to which register at which program counter. In addition, it contains information on which variable has which static type. From the addition or the load instruction in line 3 our approach can extract the index of the virtual function in the vtable. With this information, querying the DWARF debug information yields a set of possible call targets, restricted by the static type. At the end, we can add the call targets to the branch instruction.

Querying for the possible call targets consists of two parts. In the first part, a query has to collect all implementations in classes that extends the given static type. Since the dynamic type can at most be equal to the static type, we need a second part. Here, the query needs to add the implementation of the function in static type. If there is none, it has to look for its parents in the inheritance hierarchy. This is similar to the first part, but with the difference that this query recurs only until it finds the first implementation. The first part of the query analyses the children in the hierarchy, but recurs through the whole hierarchy. The reason for this difference is that the static type is a bound on the dynamic type, but only upwards the hierarchy.

Traditionally, a value analysis tries to find out about these call targets, but this has limitations that our approach surpasses. The value analysis has to keep separate values for every possible dynamic type. For our approach, the value analysis can be more abstract and – as presented in the Evaluation – even such a simple value analysis can still refine some results from our approach. A value analysis cannot find any call targets if the creation of the corresponding objects lies outside the analysed part of the program. Our approach only uses the local information at the call site and the DWARF debug information. Therefore, it needs no knowledge about the creation of the object.

#### 3. EVALUATION

We evaluated an implementation of our approach on a set of example programs. In this paper, we only present two of these examples.

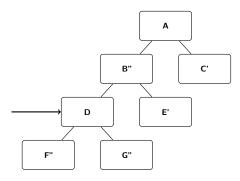

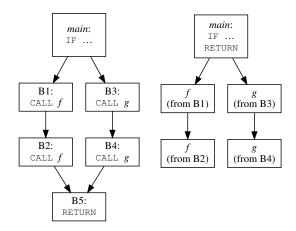

Figure 6 shows the inheritance hierarchy of one of our examples and where we have implementations of our function of interest. An additional mark shows where in this hierarchy we can find the static type of the variable, via which we call the function. Our approach adds the implementations from B, F and G to the call graph and omits the implementations in C and E. This is a safe and precise approximation. If the dynamic type for this call is different from D, a following value analysis might declare a call to the implementation in B infeasible. An approach that cannot use the whole inheritance hierarchy has to add all five implementations instead of three.

In the example program in Figure 7, the DWARF debug information knows only the static type of **this**. Therefore, our approach adds two possible call targets to the call graph, the implementations from both classes. If we want to analyse the whole program, then it is already guaranteed that this call will call the implementation in class "Derived". A simple value analysis on a graph containing both targets from above can declare the superfluous call edge infeasible.

Figure 6: Inheritance hierarchy of an example program. A is the most general class. A virtual function has an implementation in the highlighted classes. The implementations in the double highlighted classes are part of a precise solution. We call the function via a variable of static type "D".

```

class Base {

1

2

public:

3

virtual void functionA()

4

5

6

void functionB()

7

8

this->functionA();

9

10

};

11

class Derived : public Base {

12

13

public:

void functionA()

14

15

16

Base::functionA();

17

18

};

19

int main(int argc, char** argv) {

20

21

Derived derived;

22

derived.functionB();

23

24

return 0;

25

```

Figure 7: Program where the static and the dynamic type of "this" differ. The call in "functionB" calls the implementation of "functionA" in class "Derived"

#### 4. RELATED WORK

Both the works of Jones [2] and Shivers [4] introduce control flow analysis (CFA) considering functional and object oriented programming languages. Their work can resolve computed calls, but they have additional information available since they work on source code.

In [1] Dewey and Giffin present an analysis that finds vtable escape vulnerabilities. They search for a pattern of an invocation of a constructor to find vtables. Since we have to be able to analyse parts of programs, we cannot find all vtables with their method.

In [3], Köster finds that it is hard to interconnect program points on source code level and their corresponding instructions on binary level. Current techniques only allow for a mapping between entry and exit points of functions.

In [5], the DWARF debug information is used to find the addresses of vtables. However, they assume code for which the compiler will never produce the computed calls that we want to analyse.

In [6] Tröger and Cifuentes present a static analysis that finds the call sites of computed calls, but for the call targets, they use a dynamic analysis at run time.

#### 5. CONCLUSIONS AND FUTURE WORK

From our examples, we can conclude that our approach is effective. For profound conclusions about its efficiency, we need more real world example programs. Since our approach only looks at small portions of the program under analysis, the efficiency only depends on the size of the inheritance hierarchy. The size of the overall program has no direct influence. For the precision, we have to compare our results against the results of a more expensive value analysis. However, our examples cover all the scenarios that can occur in real programs, but real-world programs, in addition, have different importance and frequency for those different scenarios.

In the future, we plan to examine more instruction sequences for computed calls on other platforms. Furthermore, we plan to perform more experiments.

## 6. REFERENCES

- [1] D. Dewey and J. T. Giffin. Static detection of C++ vtable escape vulnerabilities in binary code. In *NDSS*. The Internet Society, 2012.

- [2] N. D. Jones. Flow analysis of lambda expressions. Springer, 1981.

- [3] M. Köster. Interconnecting Value Analysis Results at the Source and Binary Level. Bachelor's thesis, Saarland University, 2010.

- [4] O. Shivers. Control flow analysis in scheme. In ACM SIGPLAN Notices, volume 23, pages 164–174. ACM, 1988.

- [5] Y. Terashima and K. Gondow. Static Call Graph Generator for C++ using Debugging Information. In Software Engineering Conference, 2007. APSEC 2007. 14th Asia-Pacific, pages 127–134. IEEE, 2007.

- [6] J. Tröger and C. Cifuentes. Analysis of Virtual Method Invocation for Binary Translation. In A. van Deursen and E. Burd, editors, WCRE, pages 65–74. IEEE Computer Society, 2002.

# Schedulability-Oriented WCET-Optimization of Hard Real-Time Multitasking Systems\*

Arno Luppold and Heiko Falk

Institute of Embedded Systems / Real-Time Systems

Ulm University

{arno.luppold|heiko.falk}@uni-ulm.de

## **ABSTRACT**

In multitasking hard real-time systems, each task's response time must provably be lower than or equal to its deadline. If the system does not hold all timing constraints, WCET-oriented optimizing compilers can be used to improve each task's worst-case runtime behaviour. However, current optimizations do not account for a system's schedulability contraints. We provide an approach based on Integer-Linear Programming (ILP) for schedulability-oriented WCET optimization of hard real-time systems.

#### 1. INTRODUCTION

One of the main issues for the compiler is to determine which tasks should be optimized to which amount in order to achieve a schedulable system while complying with the limited hardware resources on embedded platforms. Current approaches on sensitivity analysis are able to provide WCETs for each task which will result in a schedulable system. However, these approaches are performed on a systemlevel basis, without respecting the compiler's low-level optimization capabilities for each task or the system's specific hardware capabilities and restrictions. As an example which will be used throughout this paper, many embedded platforms provide a very fast but small memory, called scratchpad memory (SPM). Putting a task into the SPM reduces its execution time, but the SPM is usually too small to keep all tasks - sometimes even too small for one complete single task. We therefore aim for integrating schedulability analysis into an optimizing WCET-aware compiler framework. The key contributions of this paper are:

- We provide an ILP-based method to determine which tasks should be optimized to which amount in order to achieve a schedulable system.

- We provide approaches on both dynamic and fixed priority based systems.

- We provide initial evaluation results which show the potential of our approach.

This paper is organized as follows: Section 2 gives a brief overview of related projects. Section 3 shows our underlying approach. In Section 4 we integrate the approach into a WCET-oriented optimizing compiler framework and provide initial evaluation results. This paper closes with a conclusion and future challenges.

#### 2. RELATED WORK

In [7], Liu and Layland proposed an iterative approach to calculate the response times of a hard real-time multitasking system.

$$r_i = c_i + \sum_{i=0}^{i-1} \left\lceil \frac{r_i}{T_j} \right\rceil \cdot c_j \tag{1}$$

In their approach, each task  $\tau_i$  is defined by a priority i, a net worst-case execution time (WCET)  $c_i$ , and the minimal period of two consecutive stimuli  $T_i$ . The system is defined to be schedulable, if each task's WCRT  $r_i$  is lower than or equal to its deadline  $d_i$ . Since then, response time analysis has been intensively studied, and more flexible task models have been proposed. Huge progress has been made to provide tight bounds on event-driven task sets which are not strictly periodical [1, 5].

However, those approaches don't give hints on how an unschedulable system could be turned into a schedulable one. To the best of our knowledge, the first work covering the issue of modification of task and system parameters was [6]. In this approach, a constant factor was introduced which scaled all tasks equally up to the system's first deadline miss. Analysing how system parameters may be tuned to keep or to establish a schedulable system is called sensitivity analysis. Since that first approach, sensitivity analysis has been improved massively. A method to sustain schedulability when adding a new task to a feasible system which is scheduled using EDF is described by [11]. Arbitrary activation patterns are analyzed in [8], and [9] proposes a method to perform a sensitivity analysis on distributed systems. Additionally, theoretical approaches have been introduced for parameter tuning of rate-monotonic scheduling in [2].

Although providing a system-level view on a system's sensitivity and robustness, those approaches either focus on task stimuli relaxation or do not offer clear optimization hints for optimizing compilers. They do offer sets of valid system parameters but the system engineer is still required to manually choose a set and try and optimize the tasks accordingly. Depending on the system's size, this may result in a tedious challenge. We therefore aim at providing a new approach which can be tightly coupled to both existing and future WCET-oriented compiler optimizations, allowing for a largely automated design and compilation of hard embedded real-time systems.

<sup>\*</sup>This work was partially supported by Deutsche Forschungsgesellschaft (DFG) under grant FA 1017/1-2

#### 3. APPROACH

## 3.1 Task Model

At the current state of our work we focus on strictly periodical preemptive systems. A task  $\tau_i$  is defined by its WCET  $c_i$ , its deadline  $d_i$ , period  $p_i$  and execution period  $T_i$ . We currently assume that each task's deadline d is lower than or equal to its respective period T. In case of fixed priorities, the index i denotes the task's priority, with 0 being the highest priority. We assume all timing values to be integers. This may be achieved without loss of generality e.g., by using CPU clock cycles as time unit.

## 3.2 ILP Model

We use the formulation provided by [10] which models the WCET of a task using integer-linear constraints. A task is split into its basic blocks, which are defined as an instruction sequence that must be traversed from top to bottom. Therefore, e.g., any branch instruction must be the very last instruction of a basic block. Variables are introduced for each basic block's execution time. The accumulated execution time  $w_i$  of a basic block i is defined to be greater than or equal to i's execution  $v_i$ , plus the accumulated execution time of its successor j:

$$w_i \ge v_i + w_j \tag{2}$$

Multiple successors are described by using multiple constraints. The ILP can then be solved using an objective function which tries to minimize the accumulated execution time of a task's entry block. This block provides a safe overapproximation of the task's WCET. The model can be accompanied by further constraints to perform ILP-based WCET optimizations. E.g., [3] used the model to perform a WCET-oriented scratch-pad memory (SPM) allocation. They perform static timing analysis on a given program, once with the whole program in slow Flash memory resulting in a worst-case execution time  $v_{i,F}$  for each basic block, and once with the whole program being assigned to the SPM, resulting in  $v_{i,S}$ . Eq. (2) may then be extended to

$$w_i \ge v_{i,F} - b_i \cdot (v_{i,F} - v_{i,S}) + w_i$$

(3)

$b_i$  denotes a binary decision variable which is set to 1 if the block is located in SPM, and 0 else. Additional constraints are added to respect the SPM's overall size and additional jump instructions. Without size constraints, the ILP solver would simply assign the whole program to the SPM. When minimizing the accumulated execution time of the program's entry block  $w_0$ , the ILP solver will minimize the overall WCET of the whole program. Additionally,  $w_0$  will be a safe overapproximation of the program's WCET. In a multitasking environment  $w_0$  corresponds to the task's WCET c. Our approach integrates the model by Suhendra et.al. and illustrates its usage using a slightly improved version of the SPM allocation as an example for multitasking optimizations. The improvements are mostly technical and will therefore not be discussed any further.

## 3.3 Dynamic Priority Systems

We will consider systems which are scheduled using Earliest Deadline First (EDF). For a system which is scheduled using EDF, [7] shows that the system is schedulable iff

$$\sum_{i} \frac{c_i}{T_i} \le 1 \tag{4}$$

With  $c_i$  being the WCET of task i and  $T_i$  being the minimal period between two consecutive task executions.

For dynamic priority systems where each task's deadline equals its period, the system may easily be optimized in a schedulability oriented approach by choosing Eq. (4) as the ILP's objective function. If the optimized system's workload is lower than or equal to 1, the system is schedulable using EDF. Timing overheads inflicted by the task scheduler may be modeled by additional tasks.

#### 3.4 Fixed Priority Systems

Currently our approach for fixed priority systems covers periodical systems, but should be adaptable to more complex systems like event triggered multitasking systems. We define a set of n tasks  $\tau_i, 0 \le i \le n-1$ , each with a period  $T_i$ , a WCET  $c_i$ , and deadline  $d_i$ .  $\tau_0$  is defined as the highest priority task and  $\tau_{n-1}$  the lowest priority task, respectively.  $r_i$  is defined as the WCRT of  $\tau_i$ , i.e., the maximum time span between a task becoming ready for execution and its end of execution, including all blocking times by other tasks. In a first step, response time analysis is performed by iterating over eq. (1) until one of the following conditions occurs:

- The resulting  $r_i$  does not change for any  $\tau_i$ , and each  $\tau_i$ ,  $r_i \leq d_i$ . In this case, the system is schedulable and no further steps have to be performed.

- The resulting r<sub>i</sub> does not change for any τ<sub>i</sub>, but for at least one task τ<sub>i</sub>, r<sub>i</sub> > d<sub>i</sub>. In this case, the system is stable but is not schedulable.

- At least one r<sub>i</sub> might get larger than the task's period T<sub>i</sub>. In this case, the fix point iteration is aborted and the system is said to be unstable.

We define the maximum number of preemptions of a task  $\tau_i$  by another task  $\tau_j$  as  $p_{i,j}$ . If the task is not stable, we define  $p_{i,j}$  to be the maximum allowed number of preemptions:

$$p_{i,j} = \begin{cases} \left\lceil \frac{r_i}{T_j} \right\rceil & \text{if } r_i \le T_i, j < i \\ \left\lceil \frac{d_i}{T_j} \right\rceil & \text{if } r_i > T_i, j < i \\ 0 & \text{if } j \ge i \end{cases}$$

(5)

Based on eq. (1), the schedulability of a system can be expressed as a set of inequations:

$$c_{0} \leq d_{0}$$

$$c_{1} + \left\lceil \frac{r_{1}}{T_{0}} \right\rceil c_{0} \leq d_{1}$$

$$c_{2} + \left\lceil \frac{r_{2}}{T_{0}} \right\rceil c_{0} + \left\lceil \frac{r_{2}}{T_{1}} \right\rceil c_{1} \leq d_{2}$$

$$...$$

$$c_{n-1} + \left\lceil \frac{r_{n-1}}{T_{0}} \right\rceil c_{0} + ... + \left\lceil \frac{r_{n-1}}{T_{n-2}} \right\rceil c_{n-2} \leq d_{n-1} \qquad (6)$$

The system is schedulable if all equations hold. We establish linearity by substituting  $\left\lceil \frac{r_i}{T_j} \right\rceil c_j$  with the precalculated  $p_{i,j}$ . The WCETs  $c_i$  are left as ILP variables and may be adapted to achieve a schedulable system. Our approach will now optimize the system performing the following steps:

1. Calculate the maximum number of preemptions  $p_{i,j}$  for the original system, as described in eq. (5).

- 2. Create an ILP as shown in equation (6).

- 3. Solve the ILP, with eq. (7) as the ILP's objective function. The ILP will provide a  $c_i$  for each task i.

- 4. Re-calculate all  $p_{i,j}$  with the newly calculated  $c_i$

- 5. Modify the ILP as shown in eq. (8) and calculate the relaxed WCETs  $c_{i,relaxed}$ .

- Generate the new objective function for any subsequent WCET optimizations, and perform the optimization itself.

To avoid a quadratic problem, it is necessary to assume a constant number of preemptions during the first iteration of the ILP. This will inevitably lead to an underestimation of the maximum allowed WCET for each task. Therefore, optimizations like the aforementioned SPM allocation cannot be integrated in this step of the algorithm. To ease compiler optimizations and to reduce side effects, we use the minimization of the relative change in each task's WCET as objective. The target function will be defined as:

$$\min \sum_{i} \frac{c_{i,\text{orig}} - c_{i}}{c_{i,\text{orig}}} \tag{7}$$

$c_{i,\rm orig}$  is the original WCET of task  $\tau_i$  without any optimizations.  $c_i$  is the optimized WCET of the task which will lead to a schedulable system. Using this method, the ILP solver will propose WCETs for each task which will lead to a schedulable system, while trying to modify the WCETs as little as possible.

Next, we relax the calculated maximum WCETs: We use eq. (1) to calculate updated values for each  $p_{i,j}$ . We can now allow each  $c_i$  to increase if the increase in execution time will not change the number of maximum preemptions. To achieve this, we modify the set of linear equations from eq. (6). For each inequation, we substitute the task's deadline on the right-hand side of the inequation by

$$\min\left(d_i, \left\lceil \frac{r_i}{T_0} \right\rceil T_0, ..., \left\lceil \frac{r_i}{T_{i-1}} \right\rceil T_{i-1}\right) \tag{8}$$

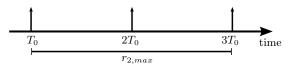

Each task's WCRT may still never exceed its deadline. As an additional constraint, the task's response time may not be larger than the minimum stimulus interval of each higher-priority task. This prevents the ILP solver from increasing a task's WCET to an amount that would allow for additional preemptions by a higher-priority task. Figure 1 illustrates this for the tasks  $\tau_2$  and  $\tau_0$  with  $\left\lceil \frac{r_2}{T_0} \right\rceil = 2$ . Given the new constraints, the ILP is solved a second time, leading to the relaxed WCET  $c_{i,relaxed}$  for each task i.

ILP constraints denoting compiler constraints like platform dependent lower bounds on each task's WCET can be directly added to the second ILP. In theory, constraints for WCET-oriented optimizations like [3] could be added as well. However, those optimizations usually do not model the architectural behaviour exactly. For complexity reasons, jump timing penalties are overapproximated, and other behaviour, like changes in the CPU's pipelines, are not modeled at all. This leads to an overapproximation of a task's WCET when moving individual basic blocks to the SPM. We use the results from our proposed sensitivity analysis to formulate a new objective function for WCET based optimizations. Given this objective function, the tasks will be

Figure 1: Maximum response time of  $\tau_2$  without additional preemptions by  $\tau_0$

optimized with regard to the system's schedulability, without need for exact WCET estimates within the optimization algorithm. Normalizing the tasks to account for different execution times and considering the necessary relative decrease in the tasks' WCET leads to:

$$\min \quad \left(\frac{\max\left(c_{0,orig},...,c_{n,orig}\right)}{c_{0},orig} \cdot \frac{c_{0,orig}}{c_{0,relaxed}} \cdot c_{0} + ... + \frac{\max\left(c_{0,orig},...,c_{n,orig}\right)}{c_{n},orig} \cdot \frac{c_{n,orig}}{c_{n,relaxed}} \cdot c_{n}\right) \quad (9)$$

This objective can now be applied to WCET-oriented compiler optimizations as proposed in [3].

## 4. EVALUATION

We illustrate the approach's performance on a set of tasks from the MRTC benchmark suite [4]. We use the WCET aware C compiler framework WCC which was also used by [3]. The target platform was chosen to be the Infineon Tri-Core 1796 micro processor running at 150MHz. The SPM size was limited to 10% of the total program size. We did not apply any standard compiler optimizations (e.g., loop unrolling) to improve comparability for the reader. All timings printed in this section were obtained using AbsInt aiT (version 14.04, build b217166). Due to the limited space in this paper, we only chose a subset of MRTC benchmarks to show the possibilities of our approach. We tried to model a realistic system with both small, but frequently executed tasks (e.g., to poll sensor values) and much larger, but less frequently called tasks (e.g., I/O operations). We chose st, lms and matmult, as they had the largest WCET out of the MRTC benchmark suite on our platform. We then randomly chose two smaller benchmarks, in this case fibcall and sqrt. To show the effects of our different optimization approaches, we chose the periods to differ by several magnitudes. For simplification reasons, we only evaluated a strictly periodic system where each task's deadline d equals its period T.

| i | Name    | T       | $c_{orig}$ | $\min \sum c_i$ | $\min \sum \frac{c_i}{T_i}$ |

|---|---------|---------|------------|-----------------|-----------------------------|

| 0 | fibcall | 50      | 4.84       | 5.62            | 2.20                        |

| 1 | sqrt    | 100     | 88.79      | 100.03          | 50.11                       |

| 2 | st      | 50,000  | 3401.87    | 2570.15         | 2481.53                     |

| 3 | lms     | 75,000  | 9125.07    | 7002.59         | 9125.07                     |

| 4 | matmult | 100,000 | 2699.29    | 1831.07         | 2699.29                     |

Table 1: Dynamic priorities, times are in  $\mu s$

Table 1 shows the WCETs for each task, without optimization, with SPM optimization which tries to minimize the sum over all WCETs, and the EDF-oriented SPM optimization. Table 3 shows the corresponding system load. It can be seen that the system is not schedulable without the SPM optimization. When applying the SPM optimization without regarding tasks' periods, the system load even goes up, because  $c_0$  and  $c_1$  increase. This somewhat strange behaviour

| P | rio. | Name    | T      | $c_{orig}$ | $c_{relaxed}$ | $c_{final}$ |

|---|------|---------|--------|------------|---------------|-------------|

|   | 0    | fibcall | 50     | 4.84       | 4.84          | 4.84        |

|   | 1    | sqrt    | 100    | 88.79      | 54.99         | 51.35       |

|   | 2    | st      | 50000  | 3401.87    | 3401.87       | 3401.87     |

|   | 3    | lms     | 75000  | 9125.07    | 9124.61       | 7002.59     |

|   | 4    | matmult | 100000 | 2699.29    | 2699.29       | 2699.29     |

Table 2: Fixed priorities, times are in  $\mu s$ .

|                     | Load |

|---------------------|------|

| Unopt.              | 1.20 |

| $\min \sum c_i$     | 1.27 |

| $\min \sum c_i/T_i$ | 0.74 |

| Opt. Fixed Prio.    | 0.79 |

Table 3: System Load

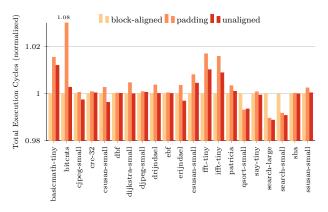

stems from the fact that the TriCore processor performs instruction fetches on 64bit memory block boundaries. The SPM optimization moves parts of the larger tasks st, lms and matmult to the SPM, therefore instruction addresses of the unoptimized tasks fibcall and sqrt change and cause a change in the system's instruction fetch behaviour, leading to an increase of the tasks' WCET. The ILP formulation of the optimization does not account for this, and is therefore not aware of the increase in the tasks' WCET. This is a purely random phenomenon which did not occur on the fixed priority optimization (compare Table 2). When applying the EDF-oriented optimization which tries to minimize the system load, it can be observed that the load drops to 0.74, thus resulting in a schedulable system.

The results for the fixed priority optimization are shown in Table 2. The 5th column, labeled  $c_{relaxed}$ , shows the target WCET for each task, as it is calculated by subsequently calling the ILP as discussed in section 3.4. It can be seen that only the tasks  $\tau_1$  and  $\tau_3$  are to be optimized. For the SPM optimization we used, the SPM model only allows either to keep or to decrease a task's WCET. We take this into consideration and adapt eq. (9) by only adding those tasks, of which the WCET must be reduced. This results in the following objective function:

$$\min\left(\frac{9125.07}{88.79} \frac{88.79}{54.99} c_1 + 1 \cdot \frac{9125.07}{9124.61} c_3\right) \approx \min\left(166c_1 + c_3\right)$$

(10)

Table 4 shows the resulting response times. We compared the response times using the approach for fixed priority systems with the response times which would arise if the tasks which were optimized for EDF were scheduled using fixed priorities. Due to the different optimization targets, the response times are higher when using the fixed priority approach. However, that approach may be adapted for systems which are not strictly periodical. In this example, both approaches lead to a schedulable system.

## 5. FUTURE CHALLENGES

We provided an approach to adapt single-task WCET-oriented compiler optimizations to achieve schedulability of multitasking hard real-time systems. Future work will cover an improved optimization strategy for fixed priority tasks, as well as profound analysis of the suboptimality which is inherent for fixed priority systems. We will analyse, if, and under

| Name    | r opt dyn. | r fixed  | Deadline |

|---------|------------|----------|----------|

| fibcall | 2.2        | 4.84     | 50       |

| sqrt    | 54.51      | 61.03    | 100      |

| st      | 5479.77    | 8772.81  | 50,000   |

| lms     | 25562.02   | 26761.40 | 75,000   |

| matmult | 31477.60   | 33671.99 | 100,000  |

Table 4: Response time using RMS, times are in  $\mu s$

which circumstances, the fixed priority approach will outperform the system load oriented approach. Additionally, we are currently working at integrating the fixed priority approach into event-based systems to perform an improved optimization of systems which are not strictly periodical. In the long run, we are planning on extending the approach to cover scheduler overheads and inter-task dependencies like cache-related preemption delays.

#### 6. REFERENCES

- [1] K. Albers and F. Slomka. An event stream driven approximation for the analysis of real-time systems. In *Proceedings of ECRTS*, pages 187–195, 2004.

- [2] E. Bini, M. Di Natale, and G. Buttazzo. Sensitivity analysis for fixed-priority real-time systems. *Real-Time Systems*, 39:5–30, 2008.

- [3] H. Falk and J. C. Kleinsorge. Optimal Static WCET-aware Scratchpad Allocation of Program Code. In *Proceedings of DAC*, pages 732–737, 2009.

- [4] J. Gustafsson, A. Betts, A. Ermedahl, and B. Lisper. The Mälardalen WCET Benchmarks – Past, Present and Future. In B. Lisper, editor, Proceedings of the International Workshop on Worst-Case Execution Time Analysis (WCET), pages 137–147, 2010.

- [5] R. Henia, A. Hamann, M. Jersak, R. Racu, K. Richter, and R. Ernst. System level performance analysis - the SymTA/S approach. *Proceedings of Computers and Digital Techniques*, 152(2):148–166, 2005.

- [6] J. Lehoczky, L. Sha, and Y. Ding. The rate monotonic scheduling algorithm: exact characterization and average case behavior. In *Proceedings of RTSS*, pages 166–171, 1989.

- [7] C. L. Liu and J. W. Layland. Scheduling Algorithms for Multiprogramming in a Hard-Real-Time Environment. *Journal of the ACM (JACM)*, 20(1):46–61, 1973.

- [8] M. Neukirchner, S. Quinton, T. Michaels, P. Axer, and R. Ernst. Sensitivity Analysis for Arbitrary Activation Patterns in Real-time Systems. In Proceedings of DATE, pages 135–140, 2013.

- [9] R. Racu, A. Hamann, and R. Ernst. Sensitivity Analysis of Complex Embedded Real-Time Systems. Real-Time Systems, 39:31–72, 2008.

- [10] V. Suhendra, T. Mitra, A. Roychoudhury, et al. WCET Centric Data Allocation to Scratchpad Memory. In *Proceedings of RTSS*, pages 223–232, 2005.

- [11] F. Zhang, A. Burns, and S. Baruah. Sensitivity analysis of arbitrary deadline real-time systems with EDF scheduling. *Real-Time Systems*, 47:224–252, 2011

# Accounting for Cache Related Pre-emption Delays in Hierarchical Scheduling with Local EDF Scheduler

Will Lunniss

Department of Computer Science

University of York

York, UK

wl510@york.ac.uk

Sebastian Altmeyer Computer Systems Architecture Group University of Amsterdam Netherlands altmeyer@uva.nl Robert I. Davis

Department of Computer Science

University of York

York, UK

rob.davis@vork.ac.uk

## **ABSTRACT**

Hierarchical scheduling provides a means of composing multiple real-time applications onto a single processor such that the temporal requirements of each application are met. This has become a popular technique in industry as it allows applications from multiple vendors as well as legacy applications to co-exist in isolation on the same platform. However, performance enhancing features such as caches mean that one application can interfere with another by evicting blocks from cache that were in use by another application, violating the requirement of temporal isolation. In this paper, we present some initial analysis that bounds the additional delay due to blocks being evicted from cache by other applications in a system using hierarchical scheduling when using a local EDF scheduler.

## 1. INTRODUCTION

Hierarchical scheduling provides a means of composing multiple applications onto a single processor such that the temporal requirements of each application are met. This is driven by the need to re-use legacy applications that once ran on slower, but dedicated processors. Each application, referred to as a component, has a dedicated server. A global scheduler then allocates processor time to each server, during which the associated component can use its own local scheduler to schedule its tasks

In hard real-time systems, the schedulability of each task must be known offline in order to verify that the timing requirements will be met at runtime. However, in pre-emptive multi-tasking systems, caches introduce additional cache related pre-emption delays (CRPD) caused by the need to re-fetch cache blocks belonging to the pre-empted task which were evicted from the cache by the pre-empting task. These CRPD effectively increase the worst-case execution time of the tasks. It is therefore important to be able to calculate, and account for, CRPD when determining if a system is schedulable or not. This is further complicated when using hierarchical scheduling as servers will often be suspended while their components' tasks are still active, that is they have started but have not yet completed execution. While a server is suspended, the cache can be polluted by the tasks belonging to other components. When the global scheduler then switches back to the first server, tasks belonging to the associated component may have to reload blocks into cache that were in use before the global context switch.

Hierarchical scheduling has been studied extensively in the past 15 years. Deng and Liu [7] were the first to propose such a two-level scheduling approach. Later Feng and Mok [8] proposed the resource partition model and schedulability analysis based on the supply bound function. Shin and Lee [16] introduced the concept of a temporal interface and the periodic resource model, and refined the analysis of Feng and Mok. When using a local EDF scheduler, Lipari *et al.* [11] [12] have investigated allocating server capacity to components, proposing an exact solution.

Recently Fisher and Dewan [9] have developed a polynomial-time approximation with minimal over provisioning of resources.

Hierarchical systems have been used mainly in the avionics industry. For example, the ARINC 653 standard [2] defines temporal partitioning for avionics applications. The global scheduler is a simple Time Division Multiplexing (TDM), in which time is divided into frames of fixed length, each frame is divided into slots and each slot is assigned to one application.

Analysis of CRPD uses the concept of *useful cache blocks* (UCBs) and *evicting cache blocks* (ECBs) based on the work by Lee *et al.* [10]. Any memory block that is accessed by a task while executing is classified as an ECB, as accessing that block may evict a cache block of a pre-empted task. Out of the set of ECBs, some of them may also be UCBs. A memory block m is classified as a UCB at program point  $\rho$ , if (i) m may be cached at  $\rho$  and (ii) m may be reused at program point q that may be reached from  $\rho$  without eviction of m on this path. In the case of a pre-emption at program point  $\rho$ , only the memory blocks that are (i) in cache and (ii) will be reused, may cause additional reloads. For a more thorough explanation of UCBs and ECBs, see section 2.1 "Pre-emption costs" of [1].

A number of approaches have been developed for calculating the CRPD when using fixed priority pre-emptive scheduling under a flat, single-level system. A summary of these approaches, along with the state-of-the-art approach is available in [1]. In 2013, Lunniss *et al.* [14] presented a number of approaches for calculating CRPD when using pre-emptive EDF scheduling.

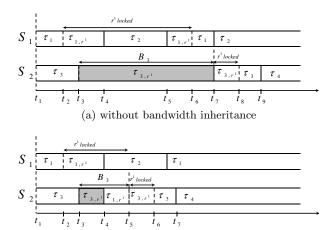

In 2014, Lunniss *et al.* [13] extended previous works to include CRPD analysis under hierarchical scheduling when using a local FP scheduler.

The remainder of the paper is organised as follows. Section 2 introduces the system model, terminology and notation used. Section 3 recaps existing CRPD and schedulability analysis. Section 4 introduces the new analysis for calculating component level CRPD incurred in hierarchical systems when using a local EDF scheduler. In section 5 the analysis is evaluated, and section 6 concludes with a summary and outline of future work.

## 2. SYSTEM MODEL

We assume a single processor system comprising m components, each with a dedicated server  $(S^1...S^m)$  that allocates processor capacity to it. We use  $\Psi$  to represent the set of all components in the system. G is used to indicate the index of the component that is being analysed. Each server  $S^G$  has a budget  $Q^G$  and a period  $P^G$ , such that the associated component will receive  $Q^G$  units of execution time from its server every  $P^G$  units of time. Servers are assumed to be scheduled globally using a non-pre-emptive scheduler, as found in systems that use time partitioning to divide up access to the processor. While a server has remaining capacity and is allocated the processor, we assume that the tasks of the associated component are scheduled using pre-emptive EDF.

The system comprises a taskset  $\Gamma$  made up of a fixed number of tasks  $(\tau_1..\tau_n)$  divided between the components. Each component contains a strict subset of the tasks, represented by  $\Gamma^G$ . For simplicity, we assume that the tasks are independent and do not share resources requiring mutually exclusive access, other than the processor.

Each task,  $\tau_i$  may produce a potentially infinite stream of jobs that are separated by a minimum inter-arrival time or period  $T_i$ . Each task has a relative deadline  $D_i$ , a worst case execution time  $C_i$  (determined for non-pre-emptive execution). We assume that deadlines are either *implicit* (i.e.  $D_i = T_i$ ) or *constrained* (i.e.  $D_i \leq T_i$ ).

Each task  $\tau_i$  has a set of UCBs, UCB<sub>i</sub> and a set of ECBs, ECB<sub>i</sub> represented by a set of integers. If for example, task  $\tau_1$  contains 4 ECBs, where the second and fourth ECBs are also UCBs, these can be represented using ECB<sub>1</sub> = {1,2,3,4} and UCB<sub>1</sub> = {2,4}. Each component G also has a set of UCBs, UCB<sup>G</sup> and a set of ECBs, ECB<sup>G</sup>, that contain respectively all of the UCBs, and all of the ECBs, of their tasks, i.e. UCB<sup>G</sup> =  $\bigcup_{\forall \tau_i \in \Gamma^G}$  UCB<sub>i</sub> and ECB<sup>G</sup> =  $\bigcup_{\forall \tau_i \in \Gamma^G}$  ECB<sub>i</sub>.

Each time a cache block is reloaded, a cost is introduced that is equal to the *block reload time* (BRT). We assume a direct mapped cache, but the work extends to set-associative caches with the LRU replacement policy as described in section 2 of [1]. We focus on instruction only caches.

# 3. EXISTING SCHEDULABILITY AND CRPD ANALYSIS

Schedulability analysis for EDF uses the *processor demand bound* function [3], [4], in order to determine the demand on the processor within a fixed interval. It calculates the maximum execution time requirement of all tasks' jobs which have both their arrival times and their deadlines in a contiguous interval of length t. Baruah et al. showed that a taskset is schedulable under EDF iff  $\forall t > 0$ ,  $h(t) \le t$ . We use a modified equation for h(t) from [14] which includes  $\gamma_{t,j}$  to represent the CRPD caused by task  $\tau_j$  that may affect any job of a task with both its release times and absolute deadlines within an interval of length t.

$$h(t) = \sum_{j=1}^{n} \left( \max \left\{ 0, 1 + \left\lfloor \frac{t - D_j}{T_j} \right\rfloor \right\} C_j + \gamma_{t,j} \right)$$

(1)

In order to determine the schedulability of a taskset in a hierarchical system, we must account for the limited access to the processor. The *supply bound function* [16], or specifically the inverse of it, can be used to determine the maximum amount of time needed by a specific server to supply some capacity c. We define the *inverse supply bound function*, *isbf*, for component G as  $isbf^G$  [15]:

$$isbf^{G}(c) = c + (P^{G} - Q^{G}) \left( \left\lceil \frac{c}{Q^{G}} \right\rceil + 1 \right)$$

(2)

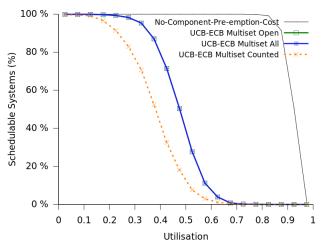

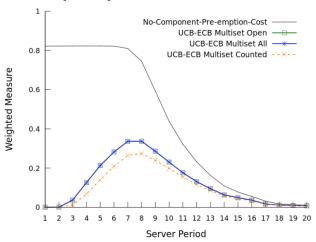

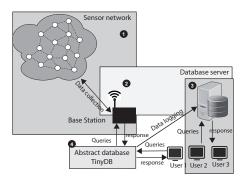

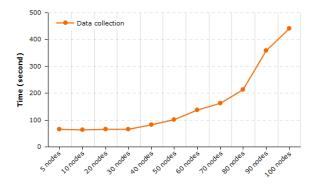

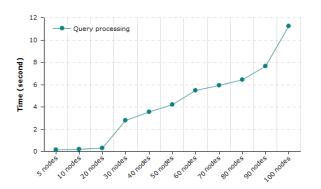

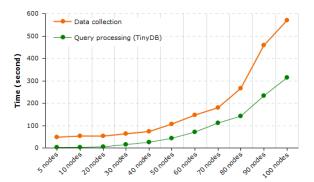

## 4. NEW CRPD ANALYSIS