# **Contents**

| Executive Summary        |    |

|--------------------------|----|

| Focus and Research Lines | 3  |

| Research Projects        | 9  |

| Highlights 2014          | 21 |

| Publications             | 43 |

| People                   | 49 |

| Facilities               | 77 |

# **Executive Summary**

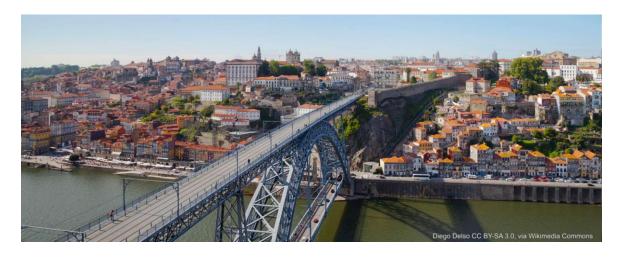

www.cister.isep.ipp.pt

The Research Centre in Real-Time and Embedded Computing Systems (CISTER) is based upon a research group created in 1997 at the School of Engineering (ISEP) of the Polytechnic Institute of Porto (IPP). Since then it has grown to become the most prominent research unit of IPP and one of the leading international research centres in real-time and embedded computing systems. In both the 2003 and 2007 evaluation processes, the CISTER was granted the classification of 'Excellent' (the highest possible mark at that time) from an international panel of experts, being the only Portuguese unit in the areas of Electrical Engineering and Computer Science and Engineering to top-rank in both evaluations.

The strategy laid out by CISTER has been from the start towards top-quality research, able to compete with the best international groups in our research areas. The research activities is focused in the analysis, design and implementation of Real-Time and Embedded Computing Systems (RTES).

The goal of CISTER is to continue to be one the International leaders of research in real-time embedded systems, and naturally reinforce such privileged position. This objective is aligned with the growing strategic importance of RTES in Europe, and the role that needs to be played in the international research landscape of the area.

CISTER is hosted by ISEP, the main management institution. Since 2011, CISTER and ISEP have entered a strategic alliance with the INESC-TEC Associated Laboratory in which CISTER became an autonomous unit of INESC-TEC. It is our belief that this allows the continuation of the synergies in a challenging future environment.

# Management Structure

The research unit is led by a Board of Directors, a Scientific Board and an External Advisory Board. The Board of Directors is led by the unit's Director and includes Vice Directors and an Adjunct Director. The main responsibilities of the Director are: to represent CISTER externally; to manage and co-ordinate the activities of the Unit; to co-ordinate the definition of the plan of activities and budget. The Scientific Board,

#### **CISTER Annual Report**

which includes all the members holding a PhD degree, has the following main responsibilities: to appoint the Director; to define the scientific research areas and working strategies; to carry out research; and to approve the plan of activities, budget and yearly report.

Board of Directors: Eduardo Tovar (Director), Luis Miguel Pinho (Vice-Director), Stefan M. Petters (Vice-Director), Filipe Pacheco (Adjunct-Director).

The activities of the unit are periodically reviewed by the External Advisory Board. Annually, interactions (including on-site visits) are organized to discuss activities, exploitation of results and future plans of the unit.

External Advisory Board: Tarek Abdelzaher, University of Illinois at Urbana-Champaign, USA; Sanjoy Baruah, University of North Carolina at Chapel Hill, USA; Alan Burns, The University of York, United Kingdom; Rodrigo Maia, Critical Software, Portugal; Daniel Mossé, University of Pittsburgh, USA; Michael Paulitsch, EADS, Germany; Sérgio Penna, Embraer, Brazil; Zlatko Petrov, Honeywell, Czech Republic; Raj Rajkumar, Carnegie-Mellon University, USA.

#### **CISTER** in Numbers

In 2014, CISTER has over 60 collaborators, covering more than 20 nationalities. Around one third of the researchers have PhD. This team has a strong and solid international reputation, built upon a robust track record of publications (70 publications in 2014), a continuous presence on program and organizing committees of international top conferences, as well as in pivotal industry-driven European projects.

CISTER is currently housed in an entirely new building exclusively devoted to its R&D activities. This single-home (2000 m2) is a strong asset to continue to compete among the best in the world in the area of RTES.

In 2014 the unit had around 1100K EUR of competitive funding. We had 8 international and industrial driven projects, and 9 fundamental research projects (FCT supported) running. We also got approved a set of new projects, accounting for a budget of 253K EUR in 2014, with a total budget of 750K EUR.

# **Focus and Research Lines**

www.cister.isep.ipp.pt/research

CISTER focuses its activity in the analysis, design and implementation of Real-Time and Embedded Computing Systems (RTES). In these systems, correctness depends not only on the logical result of computation, but also on the time at which the results are produced. This implies that, unlike more traditional information and communication systems, where there is a separation between correctness and performance, in real-time systems correctness and performance are very tightly interrelated. Furthermore, considering their tight integration with the surrounding environment, RTES require a more holistic and integrated system perspective. Historically, RTES were an important, but narrow, niche of computing systems, consisting mainly of military systems, air traffic control and embedded systems for manufacturing and process control. Meanwhile, both the emergence of large-scale distributed systems and the pervasiveness of embedded devices, enabled by advances in technology, has broaden real-time concerns into a mainstream enterprise, with clients in a wide variety of industries and academic disciplines. This trend has established RTES technology as a priority for commercial strategy and academic research for the foreseeable future and also for a wider number of applications.

RTES technologies are deployed in almost all relevant market sectors across Europe. Consequently, they have a major impact on the way these sectors work and collaborate, how they will develop, how they are perceived by both professionals and the public, and how successful their products will be on the world market. RTES is one of the strategic research and innovation areas in Europe, with impact in very important sectors such as industrial automation, automotive, aerospace, consumer electronics, communication systems and medical systems. For many of these sectors, Europe is a world-wide reference, contrary to general-purpose computing systems, traditionally dominated by non-European organizations.

Wireless Sensor Networks (WSN)

Wireless Sensor Networks (WSNs) are triggering a new era in Information and Communication Technologies. These networks of tiny embedded computing systems are enabling a new set of large-scale monitoring and control applications such as pervasive Internet, homeland security, critical physical infrastructures monitoring, precision agriculture, environmental monitoring or intelligent transportation systems. CISTER has been assuming international leadership in the WSNs scientific area, namely on supporting Quality-of-

Service (QoS), particularly focusing on timeliness and real-time, reliability and energy-efficiency aspects. We are addressing the use of both standard and COTS technology and cutting-edge solutions designed from scratch. CISTER pursues excellence-level collaborative R&D sustained by analytical, simulation and experimental models. We have recently designed, implemented and deployed the largest WSN test-bed in Europe to date, with 300+ sensor nodes.

**Multicore Systems**

Multicores are spreading at an unprecedented rate. Today, a multicore processor is the default choice in virtually any kind of standard computing device and it is increasingly being adopted in embedded computer systems (such as cellular phones, invehicle electronics and medical instrumentation).

The use of multicores in embedded systems is complicated by the fact that many embedded computer systems have real-time requirements, that is, the time at which a program produces its result is as important as the result itself. The time at which a program computes its result depends on how computer resources (processor cores, memory, bus bandwidth, I/O devices, etc.) are shared among programs and therefore the scientific community has created a toolkit of algorithms for scheduling programs on a single processor so that

the program executes at the right time. Unfortunately, scheduling programs at the right time on a multicore is currently not well understood; in particular, there is no such well-established toolkit for multiprocessors. Researchers at CISTER are currently developing scheduling algorithms and proof techniques which makes it possible to prove at design time that deadlines will be met at runtime, even if the exact time when programs request to execute is unknown.

Cyber-Physical Systems (CPSs)

Although the IT transformation in the 20th century appeared revolutionary, a bigger change is probably yet to come. The terms "Cooperating-Objects" or "Cyber-Physical Systems (CPS)" have come to describe the research and technological effort that will ultimately efficiently allow interlinking the real world physical objects and cyberspace. Actually, the integration of physical processes and computing is not new. Embedded systems have been in place since a long time to denote systems that combine physical processes with computing.

The revolution will come from extensively networking embedded

computing devices, in a blend that involves sensing, actuation, computation, networking, pervasiveness and physical processes. Such extreme networking poses considerable technical challenges ranging from the (distributed) programming paradigms (languages still lacking temporal semantics, suitable concurrency models and hardware abstractions) to networking protocols with timeliness as a structuring concern, and including systems theory that combines "physical concerns" (control systems, signal processing, etc.) and "computational concerns" (complexity, schedulability, computability, etc.).

Adaptive Real-Time Systems

We are increasingly surrounded by computer controlled devices. Many of which are not perceived as "computers" and are called embedded systems: think of mobile phones, cars, or aircraft. Many of these systems have some sort of real-time requirements, be it responsiveness, quality of service or hard deadlines, where the miss of the latter leads to catastrophic consequences. Beyond the fact that we are more and more surrounded and dependent on such systems, there is another trend visible. Embedded systems are often networked and/or receive upgrades and extensions during the lifetime of an individual system. These may be, for example, applications downloaded to your mobile phone or an

upgrade of your motor control in a garage. A third trend is an increase in mobile systems, requiring effective power management to extend the battery lifetime.

Within this research line we address the issues associated with systems requiring temporal isolation of system parts with different criticalities, as well as systems being robust and reliable in the context of additional restrictions like available energy, changing environment or a dynamic set of tasks executed on such a system.

Real-Time Software

The current use of software as the key enabler of any real-time embedded system is increasing the often contradictory demands for attributes such as flexibility, adaptation, isolation, reliability or availability. Software infrastructure (such as languages, operating systems, middleware) and models are, more and more, a fundamental topic for system development, being transversal to application areas and research domains.

In this context, this research line addresses issues associated with the software infrastructure required for developing RTES. Our approach is to integrate advanced mechanisms within programming languages, operating systems and middleware, allowing designers and programmers to manage the increasing complexity, and flexibility requirements, simultaneously reducing common errors, and allowing isolation and verification of systems.

# **Research Projects**

www.cister.isep.ipp.pt/projects

# international & industrial briver i rojec

### Arrowhead

#### Ahead of the future

JU grant nr. 332987 ARTEMIS/0001/2012 Funding: 67.6MEUR (CISTER Funding: 207KEUR)

4 years (Mar 2013 to Feb 2017)

Our society is facing both energy and competitiveness challenges. These challenges are tightly linked and require new dynamic interactions between energy producers and energy consumers, between machines, between systems, between people and systems, etc. Cooperative automation is the key for these dynamic interactions and is enabled by the technology developed around the Internet of Things and Service Oriented Architectures.

The objective of the Arrowhead project is to address the technical and applicative challenges associated to cooperative automation: provide a

technical framework adapted in terms of functions and performances; propose solutions for integration with legacy systems; implement and evaluate the cooperative automation through real experimentations in applicative domains: electro-mobility, smart buildings, infrastructures and smart cities, industrial production, energy production and energy virtual market; point out the accessible innovations thanks to new services; lead the way to further standardization work.

The strategy adopted in the project has four major dimensions: an innovation strategy based on business and technology gap analysis paired with a market implementation strategy based on end users priorities and long term

technology strategies; application pilots where technology demonstrations in real working environments will be made; a technology framework enabling collaborative automation and closing innovation critical technology gaps; an innovation coordination methodology for complex innovation "orchestration"

Partners of the Arrowhead consortium include, among others:

### CarCoDe

Platform for Smart Car to Car Content Delivery

ITEA2 N° 11037, QREN N° 30345 Funding: 399KEUR (CISTER Funding: 58KEUR)

2 years (Jul 2013 to Jun 2015)

CarCoDe will develop a software platform which enables traffic service ICT ecosystems and business opportunities to be evoked. The objective is to offer a merging layer between automotive industry, traffic service operators, and third party developers. CarCoDe is an ITEA2

labeled European project. Portuguese partners are funded in the scope of a national QREN project.

Partners of the CarCoDe consortium include, among others:

# CONCERTO

Guaranteed Component Assembly with Round Trip Analysis for Energy Efficient High-integrity Multi-core Systems

JU grant nr. 333053 ARTEMIS/0003/2012 Funding: 9.56MEUR (CISTER Funding: 375KEUR)

3 years (May 2013 to Apr 2016)

Emerging embedded systems platforms harnessing new heterogeneous, multicore architectures to enable the next generation of powerful mission-critical applications are demanding across-the-board advances in all areas of design and development to fulfil their promise. The integration of component-based design with model-driven

development creates a potent combination especially capable of mastering the complexity of these new systems. CONCERTO will deliver a reference multi-domain architectural framework for complex, highly concurrent, and multi-core systems, where non-functional properties (including real-time, dependability, and energy management) will be established for individual components, derived for

the overall system at design time, and preserved by construction and monitoring at run-time.

The CONCERTO framework that will be developed in the project will integrate: Correctness-by-construction for multicore systems with innovative model-to-code transformation techniques targeted at their special characteristics. A multi-view, hierarchical cross-domain design space sufficiently rich to enable a compositional approach to the next generation of complex, heterogeneous platform architectures. Support for iterative and incremental development of multicore systems through simulation and early model-based analysis, with fully automated back propagation of results to the user model. Hardware modelling facilities equipped to cope with the new generation of heterogeneous, multicore platforms. Advances in run-time monitoring of

mission- and operation-critical nonfunctional properties such as energy consumption on partitioned and multicore processor architectures. The applicability of the CONCERTO solutions to multiple industrial domains (including aerospace, telecoms, automotive, petroleum and medical) will be ensured through the elaboration of representative industrial use cases. CONCERTO builds on the previous CHESS project results from the ARTEMIS programme, as well as the results of several other related projects.

Partners of the CONCERTO consortium include, among others:

# **DEWI**

### Dependable Embedded Wireless Infrastructure

JU grant nr. 621353 ARTEMIS/0004/2013 Funding: 39.6 MEUR (CISTER Funding: 390 KEUR)

3 years (Jan 2013 to Dec 2015)

The EU project "DEWI-Dependable Embedded Wireless Infrastructure" with 58 partners from 11 countries deals with the development of wireless sensor networks and applications. DEWI deals with more than 20 industry driven application cases for citizens and professional users. The worked out results shall in conclusion be introduced to the public in all of Europe by using clear practical demonstrations in the areas of aeronautics, automobile, railroad and building automation.

Furthermore DEWI provides essential contributions to interoperability, standardization and certification of wireless sensor networks and wireless communication.

### HiPEAC 3

European Network of Excellence on High Performance and Embedded Architecture and Compilation

FP7-ICT-287759 Funding: 3.8 MEUR

3 years (Jan 2013 to Dec 2015)

As part of the research coordination program, HiPEAC3 includes a new instrument, called Thematic Sessions. A Thematic Session is a natural evolution of the clusters and task forces in HiPEAC2, but more reactive and selforganized. In HiPEAC3, any partner or member can propose a thematic session, on condition that it is related to the HiPEAC vision. A thematic session is comparable to an informal workshop. Proposers of a thematic session are encouraged to involve the FP7 projects and HiPEAC companies in the session they propose. In that sense a thematic session is very similar to the organization of a cluster meeting in HiPEAC2. Collaboration and networking between member institutions and across the different disciplines: computer architects, design tool builders, compiler builders, system designers, between researchers from academia and industry, between

European and non-European institutions. This collaboration between best of breed must lead to more European excellence in the HiPEAC domain. Collaboration and networking is stimulated by various networking events, and the small collaboration incentives like collaboration grants, mini-sabbaticals, internships.

Valorisation of research results in the form of highly visible publications and commercialization of research results by existing companies or by newly created companies. The goal is to help companies to achieve world-leading positions in the computing systems and computing products, and to further increase Europe's worldwide visibility in the domain via the HiPEAC conference, the ACACES summer school, the HiPEAC journal, a newsletter, a website, seminars, technical reports, workshops, and awards.

### EMC<sup>2</sup>

Embedded multi-core systems for mixed criticality applications in dynamic and changeable real-time environments

JU grant nr. 621429 | ARTEMIS/0001/2013 Funding: 94.6MEUR (CISTER Funding: 307KEUR)

3 years (Apr 2014 to Mar 2017)

EMC2 – 'Embedded Multi-Core systems for Mixed Criticality applications in dynamic and changeable real-time environments' is an ATREMIS Joint Undertaking project in the Innovation Pilot Programme 'Computing platforms for embedded systems' (AIPP5). Embedded systems are the key innovation driver to improve almost all mechatronic products with cheaper and even new functionalities. They support today's information society as intersystem communication enabler. A major industrial challenge arises from the need to face cost efficient integration of different applications with different levels of safety and security on a single computing platform in an open context. The objective of EMC2 is to establish Multi-Core technology in all relevant Embedded Systems domains. EMC2 is a project of 97 partners of embedded

industry and research from 19 European countries and Israel with an effort of about 800 person years and a total budget of about 100 million Euro.

### P-SOCRATES

Parallel SOftware framework for time-CRitical mAny-core sysTEmS

FP7-ICT-611016

Funding: 2.76MEUR (CISTER Funding: 544KEUR)

3 years (Oct 2013 to Sep 2016)

The recent technological advancements and market trends are causing an interesting phenomenon towards the convergence of High-Performance Computing (HPC) and Embedded Computing (EC) domains. On one side, new kinds of HPC applications are being required by markets needing huge amounts of information to be processed within a bounded amount of time. On the other side, EC systems are increasingly concerned with providing higher performance in real-time, challenging the performance capabilities of current architectures. The advent of next-generation many-core embedded platforms has the chance of intercepting this converging need for predictable high-performance, allowing HPC and EC applications to be executed on efficient and powerful heterogeneous architectures integrating generalpurpose processors with many-core

computing fabrics. To this end, it is of paramount importance to develop new techniques for exploiting the massively parallel computation capabilities of such platforms in a predictable way.

P-SOCRATES will tackle this important challenge by merging leading research groups from the HPC and EC communities. The time-criticality and parallelisation challenges common to both areas will be addressed by proposing an integrated framework for executing workload-intensive applications with real-time requirements on top of next-generation commercial-off-the-shelf (COTS) platforms based on many-core accelerated architectures. The project will investigate new HPC techniques that fulfil real-time requirements.

The main sources of indeterminism will be identified, proposing efficient mapping and scheduling algorithms, along with the associated timing and

# **CISTER Annual Report**

schedulability analysis, to guarantee the real-time and performance requirements of the applications.

Partners of the P-SOCRATES consortium include, among others:

cost-effective certification and recertification of mixed-criticality, component based, multi-core systems.

**Fundamental Research Projects**

## **AVIACC**

Analysis and Verification of Concurrent Critical Programs

FCOMP-01-012244-FEDER-020486 PTDC/EIA-CCO/117590 Funding: 94KEUR (CISTER Funding: 24.1KEUR)

3 years (May 2012 to Apr 2015)

The goal of the project is to extract models from concurrent programs and

building an automatic framework for checking (temporal) properties using verification technologies, both static and run-time

# **MASQOTS**

Mobility mAnagement in wireless Sensor networks under QoS constraints using standard and Off-The-Shelf technologies

FCOMP-01-0124-FEDER-014922 PTDC/EEA-TEL/112220/2009 CISTER Funding: 94.8KEUR

42 months (Feb 2011 to Jul 2014)

MASQOTS aims at real-time and reliable communications in IEEE 802.15.4/ZigBee (15.4/ZigBee, for short) Wireless Sensor Networks (WSNs) supporting physical mobility. Physical mobility concerns mobile sensor/actuator nodes and node groups (e.g. body sensor networks (BSNs),

robots), and also mobile sinks (e.g. gateways, user-interface equipment).

The main objective of this project is to design a real-time and reliable mobility management mechanism for IEEE 802.15.4/ZigBee-based WSNs.

We will build upon the most widespread WSN technologies – the 15.4 and ZigBee protocols and the TinyOS operating system (OS) – for which the research team in this proposal is international leader. OnWorld predicts that in 2012, 88.3% of the WSN units will be standards-based. Freescale reports over 7 million 15.4/ZigBee units sold in 2008 and In-Stat forecasts 292 million units in 2012. TinyOS is the most used OS for WSNs.

MASQOTS will also address some fundamental (not yet solved) problems, such as the ones related to reliable Radio Link Quality Estimation (LQE), efficient and dynamic resource management, reliable and time-bounded handoff and re-association mechanisms and the provision of (simulation, analytical) models/tools for WSN analysis and dimensioning.

### **PATTERN**

Programming AbsTracTions for wireless sEnsor Networks

FCOMP-01-0124-FEDER-028990 PTDC/EEI-SCR/2171/2012 CISTER Funding: 149KEUR

28 months (Jun 2013 to Sep 2015)

In this project, we aim to tackle two critical challenges for the future success of WSN: (i) provide a seamless model for the development of correct applications, whilst (ii) efficiently managing and isolating multiple independent applications.

Our WSN model and framework will seamlessly deploy multiple independent applications on a heterogeneous sensing infrastructure, coordinating computations, packet delivery and data aggregation to reduce overall resource usage. The programming framework is based on a macro programming approach and includes high-level

programming abstractions. We plan to co-design the programming framework with adequate design patterns (a widely accepted software engineering approach).

We claim that such developments are crucial for future WSN and will be beneficial in many usage scenarios. This project particularly targets the use-case of modern smart buildings One important aspect of this application domain is that different users might develop them at different times, and it is not practical to merge them into a single application.

## **REGAIN**

Real-time scheduling on general purpose graphics processor units

FCOMP-01-0124-FEDER-020447 PTDC/EIA-CCO/118080/2010 CISTER Funding: 139KEUR

40 months (Apr 2012 to Jul 2015)

Among all processors sold today, 98% are used in embedded computer systems; therefore, catering to this segment is of utmost importance.

Moreover, there is a persistent trend in computing that techniques originally developed at the high-end (pipelining, cache-memories, instruction-level parallelism) later propagate to embedded computer systems. Graphics processors are the next technology to do this transition.

Therefore, this project will create a real-time scheduling theory for GPGPUs. This theory will offer (i) a model suited for describing real-time scheduling on GPGPUs, (ii) algorithms for run-time scheduling of tasks using GPGPUs and (iii) algorithms for proving, before run-time, that tasks using GPGPUs meet their deadlines. This project will also test the theory on commercially available GPGPUs.

## RePoMuc

Real-time Power management on partitioned MultiCores

FCOMP-01-0124-FEDER-015050 PTDC/EIA-EIA/112599/2009 CISTER Funding: 106KEUR

3 years (Feb 2011 to Jan 2014)

The fundamental objective of the RePoMuC project to provide a methodology for real-time power-management in Multicores, considering: 1. the non-linear behaviour of dynamic frequency and voltage scaling (DVFS) on execution-time and energy, 2. pre-emption delays, and 3. memory bus contention Particular focus will be given to demonstrate with a real-world implementation the practicality and

limitations of the proposed methodology. The approach I intend to take is to build on successful experience of the group in the areas of DVFS power management, real-time multiprocessor scheduling and temporal isolation. The issues of DVFS behaviour, pre-emption delays, and memory bus contention have a fundamental communality in the sense that they are all tightly coupled to the amount of memory traffic.

### **SMARTS**

### Slack Management in Hierarchical Real-Time Systems

FCOMP-01-0124-FEDER-020536 PTDC/EIA-CCO/121904/2010 CISTER Funding: 158KEUR

42 months (Apr 2012 to Sep 2015)

Most of modern computing systems are embedded with the physical environment. When such embedded systems are additionally subject to temporal constraints they are termed real-time systems.

There are a number of relevant trends in real-time systems: the complexity of such systems increases dramatically, often leading to integration of subsystems from various vendors; real-time and best effort applications may share the processor on a given device; the software on such systems may be subject to change leading to dynamic real-time systems.

A widely accepted design paradigm for such complex systems is component-based engineering in which 1) the system is first decomposed into simpler and smaller applications, 2) applications are independently designed and analysed, and 3) applications are composed together to generate the system. Depending on how the

applications are grouped together for composition, the resulting system can be represented as a tree of applications; each parent-children pair denotes a composition where the childapplications were composed together to form the parent-application.

Within this project, we will: propose to investigate a comprehensive reclamation of all slack in a hierarchical system; investigate the impact of preemption, integrate pre-emption estimation techniques and provide a framework for alternative policies. Finally, we will explore how the developed techniques can be applied in a multicore setting.

For this we will build on the work of the ViPCore project (PTDC/EIA-CCO/111799/2009) also executed in CISTER, which in turn builds in among other things on [11, 27]. The multicore development will run in parallel to the other activities once the initial work on uniprocessors have been identified.

### Smartskin

**Densely Instrumented Physical Infrastructures**

FCOMP-01-0124-FEDER-020312 PTDC/EEA-ELC/121753/2010 CISTER Funding: 141KEUR

3 years (Mar 2012 to Feb 2015)

Although the information technology transformation of the 20th century appeared revolutionary, a bigger change is on the horizon. The term Cyber-Physical Systems (CPS) has come to describe the research and technological effort that will ultimately allow the interlinking of the real-world physical objects and the cyberspace efficiently. The integration of physical processes and computing is not new.

Embedded systems have been in place for a long time and these systems often combine physical processes with computing. The revolution will come from massively networked embedded computing devices, which will allow instrumenting the physical world with pervasive networks of sensor-rich embedded computation.

In this project we intend to develop techniques and technologies that allow performing scalable and efficient data processing in large-scale dense cyber-physical systems. This is yet an unsolved problem. The major novelty of this proposal is effectively in the codesign of distributed algorithms for sensor data processing and underlying networked distributed computing systems with corresponding resource management schemes such that the utilization of resources is low.

# **VipCore**

Virtual Processor-based Multicore Scheduling

FCOMP-01-0124-FEDER-015006 PTDC/EIA-CCO/111799/2009 CISTER Funding: 111KEUR

40 months (Feb 2011 to Jun 2014)

Scheduling on multicores is a much harder problem than those studied under single processor scheduling theories, largely because of the inherent non-parallelism in workload tasks. Although a multicore platform may execute different tasks from a workload at the same time, it is typically not allowed to execute the same task on more than one core simultaneously. This project plans to research multiprocessor frameworks and platforms to tackle these issues. One important concept is the notion of virtual processors, which allow to use a

three-step scheduling strategy: partitioning of workload tasks and assigning virtual processors to each partition, scheduling of tasks on virtual processors within each cluster, and scheduling of virtual processors on the physical cores. Another important concept is the notion of pJobs, which allow tasks to be executed in parallel in the physical cores, increasing the potential parallelism of applications. The project will also research into architectures and platforms for supporting these concepts, and the underlying resource sharing paradigms.

## **V-SIS**

Sistema de Validação de Sistemas Críticos

**V-SIS**

QREN - SI I&DT Nr. 38923 CISTER Funding: 53KEUR

18 months (Jan 2014 to Jul 2015)

The technological and scientific evolution is not linear. Like a river that forms during a storm the evolution droplets accumulate up until when they gather sufficient momentum to create a torrent or change the course of a river. This landscape of change is taking place these days in the development and validation of critical systems in the automotive and aeronautics sectors. The effects of this change also propagate to sectors like medical equipment and railway. The competence to validate highly optimized and high-value critical systems is essential for an economy like Portugal that has to compete with economies that build their strength in

"brute force" with cheap labour. The V-SIS project proposes addressing this challenge with the creation of a critical systems validation competence centre, leveraging our capability to compete worldwide. The project seeks to take advantage from the landscape of change, the doubts and needs triggered by normative evolutions like the ISO26262 inception (automotive) and the upgrade to DO-178C (avionics). The V-SIS project proposes working two elemental vectors (1) functional safety and (2) critical systems validation. The work will be arranged in (i) processes innovation (RAMS techniques, model based V&V, multi-criticality systems, security fault injection) and (ii) validation laboratory development.

# **Highlights 2014**

www.cister.isep.ipp.pt/news

January

# Another ARTEMIS Project approved for 2014

DEWI (Dependable Embedded Wireless Infrastructure), another ARTEMIS project where CISTER participates was approved. This is another result of the effort developed by CISTER in the last open call for research projects in the strategic ARTEMIS initiative. DEWI is scheduled to start March 2014 and EMC2 (Embedded multi-core systems for mixed criticality applications in dynamic and changeable real-time environments) an Artemis Innovation Pilot Project (AIPP) in April 2014.

DEWI envisions to significantly foster Europe's leading position in embedded wireless systems and smart (mobile) environments such as vehicles, railway cars, airplanes and buildings. Each of these environments is reflected as a domain in the project, and CISTER's main work is in the Aeronautics domain (SP2), led by CISTER researchers. CISTER is also involved in management and architectural work in the Interoperability domain (SP6) that is responsible for finding commonalities between the several application domains.

DEWI is also a success case as it has the biggest industrial Portuguese participation in an Artemis project. Besides CISTER, the project involves Critical Software, Critical Materials and GMV.

# HiRES Workshop at HiPEAC 2014

CISTER researcher Luis Miguel Pinho co-organized the 2nd Workshop on High-performance and Real-time Embedded Systems (HiRES 2014) held in conjunction with the 9th International Conference on High-Performance and Embedded Architectures and Compilers (HiPEAC 2014).

The workshop (which occurred on January 20, 2014, in Vienna, Austria) brought together researchers and engineers in the confluence of high-performance, embedded and real-time systems for a variety of application domains. As usual, the event was fruitful with discussions on the challenges and research directions that should be tackled by the community.

The program counted with one keynote from Thorbjörn Jemander, Vision Software Architect at Autoliv Electronics (Sweden), presenting a perspective on the challenges of HPC techniques when applied to automotive critical systems. Additionally there were two sessions of technical papers on topics such as many-cores, mixedcriticality and parallelization, and a session on presentations from European R&D projects on the area. The workshop was a success, doubling the number of participants from the previous edition, and almost doubling the number of submitted papers.

# CISTER/INESC-TEC Seminar on Appliance's Energy Efficiency under Peak Power Constraints

Last January 21st, 2014 CISTER hosted another of its seminars, this time dedicated to energy efficiency. The seminar titled "Coordinated Scheduling of TCEDs under Peak Power Constraint" was given by Gopinath Karmakar from the Bhabha Atomic Research Centre, India, and addressed the problem of maintaining thermal comfort-bands associated with background loads under Peak energy consumption constraint.

Peak energy consumption has impact on upfront capital costs and hence on energy tariffs. Reducing the size of the peaks has been recognized as an important consideration in the design of efficient demand-response systems. A substantial fraction of the energy demand of buildings comes from the Thermostatically Controlled Electrical Devices (TCED) viz., air-conditioners (ACs), refrigerators and room-heaters, which do not need human interaction for their continuous operations.

So long as desirable temperature levels, referred to as thermal comfort-bands, are maintained by such background loads, users will not be concerned about when they perform their assigned functions. i.e., when they consume the energy required to function. Thermal Comfort Band Maintenance (TCBM), a new algorithm for scheduling such background loads under peak power constraint was presented as well as a discussion on how TCBM can adapt to changes in ambient parameters and provide the basis for efficient demandresponse systems.

Gopinath Karmakar is a scientist from the Bhabha Atomic Research Centre, India, which has been involved in the design and development of embedded software for safety-related systems of the Indian nuclear plants for more than two decades. His current research interest is smart grid with a focus on smart home.

# **TACLe COST Action Meeting**

CISTER researcher Konstantinos Bletsas attended the TACLe ("Timing analysis at the code level") COST Action meeting in Vienna, January 23-24, representing Portugal in the "Management Committee".

The two days meeting involved research presentations from participants and discussion in between. The meeting also included managerial sessions where

planning and decisions about the project where discussed and agreed; namely, the planning of TACLe summer school this year.

COST Actions are designed to create networks of researchers in Europe around a particular topic. In this particular case, it concerns code-level timing analysis and brings together researchers from key research organizations in Europe, like the Mälardalen University, Sweden, University of York, UK, or University of Saarbrücken, Germany.

# Arrowhead General Assembly Meeting and first review results

CISTER researchers Luis Lino Ferreira and Christos Chrysoulas participated on the Artemis AIPP Arrowhead General assembly which has been held in Budapest, on January 14th-16th.

During the meeting the participants had the chance to present, discuss and apply the Arrowhead Documentation Framework and the Arrowhead Common Framework. The former is being developed on task 7.1 led by CISTER, and the later being developed in task 7.3 and WP8, with a strong participation by CISTER.

Also during the meeting, the participants had the possibility of analyzing the very positive results of the first project review meeting and that the commission accepted all

deliverables submitted by the project consortium.

The Arrowhead project addresses cooperative automation and is enabled by the technology developed around the Internet of Things and Service Oriented Architectures. The project will provide a technical framework adapted to such systems. Implementation and evaluation will be through through real deployments in various applicative domains: electro-mobility; smart buildings; infrastructures and smart cities; industrial production; energy production and energy virtual market.

Arrowhead belongs to the first group of very large Artemis AIPP projects with an overall budget of around 90 million Euros, involving most European countries. Besides ISEP (through CISTER), the Arrowhead project involves key European industrial players such as Acciona (SP), Airbus Operations (FR), FIAT (IT), Ford (UK), Honeywell (CZ), INDRA (SP), Infineon (AT), NXP (FR), Schneider Electric (FR), STMicroelectronics (IT), and Thales (FR).

# 27th International Conference on Architecture of Computing Systems successfully held in Luebeck

CISTER/INESC-TEC researcher Eduardo Tovar served as Program co-chair of the 27th International Conference on Architecture of Computing Systems (ARCS 2014). The conference tool place in Luebeck, Germany, on February 25 -28.

The ARCS series of conferences is one of the most important and oldest scientific events for computer architecture research in Europe. It celebrated this year 40 years of tradition reporting top notch results in

#### **CISTER Annual Report**

computer architecture, operating systems and computing systems.

The focus of the 2014 conference was on embedded computer systems connecting computing with the physical world, a topic also known as Cyber-

Physical Systems. This year's highlights included a set of three high quality keynote talk, by Karl-Henrik Johansson (KTH, Sweden), Ravi Nair (IBM T. J. W Research Centre, USA) and Thomas Ludwig (German Climate Computing Centre, Germany).

# February

# European Center for Ubiquitous Technologies and Smart Cities

CISTER/INESC-TEC researchers Raghuraman Rangarajan and Eduardo Tovar attended the UBICITEC meeting held in Essen, Germany, last February 13, to discuss opportunities and possibilities of collaboration, especially with respect to Horizon 2020.

UBICITEC is the European Center for Ubiquitous Technologies and Smart Cities, founded on November 2012, as a continuation of the results obtained in the European Network of Excellence on cooperating Objects CONET (FP7). The main goal of UBICITEC is to establish a World-Class Center of Excellence on Smart Cities and Ubiquitous Technologies while increasing Europe's visibility in the areas of Ubiquitous Technologies, Internet of Things, Cooperating Objects and Cyber Physical Systems.

### March

# New highly skilled Researcher joins CISTER

CISTER/INESC-TEC has recently welcomed a new PhD member, Dorin Maxim, to its expanding international research team.

Dorin has received his Ph.D. degree in computer science in 2013 from the university of Lorraine, France after working in the renowned INRIA - Nancy Grand Est laboratory. He obtained a master degree in computer sciences (on the topic of artificial intelligence) in 2010 and a double bachelor's degree in mathematics and theoretical computer sciences in 2008, both from the Lower Danube University in Galati, Romania.

His research interests lie in the area of Real-Time Systems with particular attention to Probabilistic Analysis of Real-Time Systems. For now he will be contributing to the SMARTS (Slack management for hierarchical real-time systems in a multicore scenario) research project and will be involved in the new Artemis EMC2 project. EMC2 will start in April with CISTER/INESC-TEC teaming up with EADS, Thales, Infineon Technologies, Ericsson, BMW, Volvo, Philips Healthcare and Siemens. The Artemis EMC2 project addresses embedded multi-core systems for mixed-criticality applications in dynamic real-time environments.

# CISTER to organize highly reputed Conference on Wireless Sensor Networks: EWSN 2015

CISTER/INESC-TEC will host the 12th edition of the highly reputed European Wireless Sensor Network conference (EWSN). Being one of the leading international conferences in this area, EWSN has played a prominent role in the dissemination of innovative research and provides a high quality discussion forum.

eWSN 2015 will highlight the diversity of domains that are associated to wireless sensor networks today and welcome strong contributions to the area of wireless sensor networks, broadly defined. The conference will be an opportunity to gather researchers from all over the world, working in the forefront of research in the area, and also includes demos and poster sessions where real working systems or prototypes are shown. The hosting of this event is recognition of CISTER/INESC-TEC's contribution to this field.

The conference will be held at ISEP on February 2015.

### April

# CISTER Participates in a New Project on Validation of Critical Systems

CISTER/INESC-TEC is a partner of the V-SIS project which has been recently approved in the framework of the System of Incentives for Research and Technological Development (SI I&DT) of the National Strategic Reference Framework (QREN).

The V-SIS (Validation of Critical Systems) project proposes to address the challenge of critical systems validation through the creation of a validation competence centre, which will tackle the landscape of change and evolution in critical systems, triggered by normative evolutions like the recent ISO26262 (automotive) and the upgrade of DO-178C (avionics).

The V-SIS project proposes working two elemental vectors (1) functional safety and (2) critical systems validation. The work will be arranged in (i) processes innovation (RAMS techniques, model based V&V, multicriticality systems, security fault injection) and (ii) validation laboratory development.

The project is led by Critical Software and includes CISTER/INESC-TEC and the CISUC research centre of the University of Coimbra. CISTER/INESC-TEC's role will be in the embedded real-time domain, in particular in what concerns the challenges introduced by the new multicore platforms.

# CISTER's PhD Student Successfully Defends His Thesis

CISTER/INESC-TEC PhD student Gurulingesh (Guru) Raravi has successfully defended his PhD thesis titled "Real-Time Scheduling on Heterogeneous Multicores". Guru received his PhD with distinction from the University of Porto where he was enrolled in the PhD program jointly taught by CISTER/INESC-TEC and FEUP.

The main opponents where Prof. Sanjoy Baruah from the University of North Carolina, (USA) and Dr. Laurent George from the Laboratoire d'Informatique Gaspard-Monge at University of Paris-Est, France, both highly respected authorities in the field.

This work significantly enhanced the scheduling theory for heterogeneous multicores. Some of the specific problems addressed in this work, had no previous solutions and hence some of the proposed solutions in this work are first of their kind. Furthermore, for the problems where solutions existed before, the solutions proposed in this thesis are better than the existing solutions either in terms of the speedup factor or run-time complexity or average-case performance or a combination of these factors.

Throughout his work, Guru has managed to achieve recognition of his research as evidenced by the Outstanding paper award at 24th Euromicro Conference on Real-Time Systems (ECRTS 2012) and the Best paper award at 6th Junior Researcher Workshop on Real-Time Computing (JRWRTC 2012). Besides these awards, results of his work were published in several reputed conferences such as RTSS 2010, RTSS 2012, ECRTS 2012, etc. and also in journals such as Real-Time Systems Journal 2013, 2014.

After this fruitful collaboration with CISTER/INESC-TEC for the last 4 years, Guru will now join the highly reputed Xerox Research Institute in Bangalore, India.

# CISTER hosts two General Assembly Meetings of European Projects

Beginning of April CISTER/INESC-TEC hosted two project General Assembly meetings, for projects ENCOURAGE and CarCode.

The ENCOURAGE General Assembly meeting has been held at CISTER/INESC-TEC on the 1st and 2nd of April. The meeting accounted the presence of 17 persons, from 9 different ENCOURAGE partners. The main objective of the meeting was mainly to deal with open issues in some work packages and to prepare for final review of the project, which will be hosted by ENEL (Italy) in November 2014.

On April 3rd and 4th, CISTER/INESC-TEC hosted the General Assembly of the CarCoDe project. The goal of the meeting was a deep analysis the current status of the project and the definition of a timeline for the near future efforts.

The ENCOURAGE project, of the FP7/ARTEMIS Embedded Computing Systems Initiative, aims to develop embedded intelligence and integration technologies that will directly optimize energy usage in buildings with renewable energy and enable active participation in the future smart grid environment.

In the ENCOURAGE project, CISTER/INESC-TEC is leader of the WP8 Work package (exploitation, dissemination and standardization) and of the T2.3 task, responsible for defining the ENCOURAGE architecture and for the specification and development of the ENCOURAGE middleware (and in particular of its messaging system).

The CarCoDe project aims at creating a middleware for vehicular applications to let vehicles and infrastructure communicate in a seamless and efficient way, and demonstrators of the developed technology. The research methodology involves the simulations of protocols to disseminate and collect data from vehicles via both vehicle-tovehicle (e.g.: WAVE) and infrastructure (LTE) communication, and implementation of the middleware on On Board Units (OBUs), which are embedded systems hosted on the vehicles. The early prototypes of OBUs will communicate using the most promising options for the communication technology (wi-fi and LTE).

The consortium working on CarCoDe is built of a diverse mix of 21 partners from France, Spain, Portugal and Turkey, belonging to industry and academy alike. In particular, Airbus Defense and Space, Thales, Turkcell are leading some of the main tasks of the project.

In the context of CarCoDe, CISTER/INESC-TEC is currently finalizing the architecture for both middleware and demonstrators, and in the close future it will design a system that integrates existing OBUs in LTE infrastructure. The Portuguese partners of the consortium will implement two demonstrators, one realizing online monitoring of the status of the car, and the second to facilitate the search for an available parking spot. Moreover, CISTER/INESC-TEC is developing a simulator based on ns-3 and using WAVE and LTE modules to test the communication paradigms of vehicle-to-vehicle and infrastructure communication.

# General Chair of the 20th IEEE Real-Time Applications Symposium

Eduardo Tovar served as the General chair of the 20th IEEE Real-time and Embedded Technology and Applications Symposium (RTAS 2014) which was held in Berlin, Germany, April 15-17 as part of Cyber-Physical Systems Week.

Since 2008, CPS Week is the premier event on Cyber-Physical Systems joining five top conferences in one single location, covering complementary aspects of CPS and bringing together internationally leading researchers in this dynamic field with over 600 participants in this year edition. The 20% acceptance rate of RTAS is a strong indicator of its quality and continuous interest as a premier venue for real-time topics.

RTAS is the oldest of these events and this year it is celebrating its 20th anniversary. Besides the regular paper sessions on topics such as architectures, scheduling, mixed criticalities and memory management, there was also an Industrial session with 5 invitees from Daimler, ETAS, Kalray, Airbus Group (former EADS) and AbsInt which presented real-life case studies of practical application of real-time and embedded systems in industry.

# The largest ICT Artemis project, EMC2, has just started

The Artemis Innovation Pilot Project EMC2 (Embedded multi-core systems for mixed criticality applications in dynamic and changeable real-time environments) has just started this April 2014. During the kick-off meeting, held in Munich, Germany, on 7th and 8th of April, CISTER/INESC-TEC was represented by Eduardo Tovar.

EMC2 is the largest ICT project in Europe with nearly 100 partners and a total budget of 94 Million Euros. Infineon's CEO, Mr. Reinhard Ploss and the Bavarian Ministry of Economic Affairs and Media, Energy and Technology, State Secretary, Mr. Franz Josef Pschierer were in charge of the formal opening of the project's kick-off meeting. The agenda also included talks by the Acting Executive director of ARTEMIS and the Head of BMW Research.

EMC2 starts from the observation that the field of embedded systems is undergoing a disruptive evolution, where different types of systems and components are interconnected, thus reducing the boundaries between application domains, and placing the focus on interoperability. In addition,

the increasing use of multi- and manycore processors brings additional challenges to the development of critical and real-time applications, and the process of developing new systems is inefficient and expensive.

CISTER/INESC-TEC's team involved in the EMC2 project, led by Eduardo Tovar, will participate in several of the research activities, particularly in the work packages titled "Executable Application Models and Design Tools for Mixed-Critical, Multi-Core Embedded Systems", "Dynamic Runtime Environments and Services" and "Multi-core Hardware Architectures and Concepts", and also in two of the "Living Labs".

CISTER/INESC-TEC and Critical Software are also leading a use case in the area of automotive, and involved in the use case in the area of avionics, led by the Airbus Group. The project also includes other industrial and academic partners from renowned companies such as Ericsson, BMW, Airbus, Volvo, Philips Healthcare, Siemens, Thales and Infineon Technologies.

EMC2 is a direct result of the effort developed by CISTER/INESC-TEC in the last open call for research projects in the strategic ARTEMIS initiative alongside with the project DEWI (Dependable Embedded Wireless Infrastructure) which started in March 2014. Both projects focus on applicability and industry and it is expected that it will encourage potential technology transfer activities in the future.

# May

# New highly skilled PhD researcher joins CISTER

Sana Ullah is the most recent PhD member to join CISTER/INESC-TEC.

Sana Ullah received his Ph.D. degree in Information and Communication

Engineering from Inha University (South Korea) in 2011. He worked as an Assistant Professor in the College of Computer and Information Science, King Saud University, Riyadh from December 2011 to March 2014.

He currently serves as an editor for Springer Journal of Medical Systems, KSII Transaction of Internet and Information Systems (TIIS), Wiley Security and Communication Network (SCN), Journal of Internet Technology and International Journal of Autonomous and Adaptive Communications Systems (IJAACS).

Sana served as a guest editor for many top journals including Elsevier Journal of Information Science (INS), Springer Journal of Medical System (JOMS), and Springer Journal of Telecommunication Systems (TS). He also served as a cochair/TPC member for a number of international conferences including BodyNets, IEEE PIMRC, IEEE Healthcom, IEEE Globecom, and IEEE WCNC.

He will be developing R&D on Wireless Sensor Networks and Body Area Networks for exploitable applications and systems.

# CISTER hosted a distinguished seminar from Prof. Radu Marculescu

During the visit of Prof. Radu

Marculescu at CISTER with the main

purpose of strengthening his

collaboration with the Research Center,

he took the opportunity to give a

presentation on "Design of Future

Integrated Systems: A Cyber-physical

Systems Approach". During his talk, he

addressed some fundamental issues

related to the modeling and

optimization of power and performance

of next generation of integrated

systems while taking a cyber-physical

approach.

Radu Marculescu is a Professor in the Dept. of Electrical and Computer **Engineering at Carnegie Mellon** University, USA. He received his Ph.D. in Electrical Engineering from the University of Southern California in 1998. He has received the Donald O. Pederson Best Paper Award from the **IEEE Transactions of Computer-Aided** Design of Integrated circuits and Systems in 2012, the Best Paper Award of IEEE Transactions on VLSI Systems in 2011 and 2005, as well as several best paper awards in major conferences in the area of design automation and multi-core design. Currently, Dr. Marculescu is the Editor-in-Chief of Foundations and Trends in Electronic Design Automation and an Associate Editor of Elsevier Journal of Nano Communication Networks. In the past, he was an Associate Editor of IEEE Trans. on Computers, IEEE Trans. on Computer-Aided Design of Circuits and Integrated Systems, ACM Trans. on **Embedded Computing Systems, and**

IEEE Trans. on VLSI. He has been involved in organizing several international symposia, conferences, workshops, and tutorials, as well as guest editor of special issues in archival journals and magazines. His research focuses on design methodologies and software tools for embedded systems, cyber-physical systems, and biological systems. Radu Marculescu is an IEEE Fellow.

# Successful first review of European FP7 project led by CISTER

The P-SOCRATES (Parallel SOftware framework for time-CRitical mAny-core sysTEmS) project first Review Meeting was successfully held on May 15, at the venue of the Barcelona Supercomputing Center, Spain. The review meeting was held within the block review week, organized by the Complex Systems & Advanced Computing Unit of the **European Commission (CNECT A3)** which brought together the "Advanced Computing project cluster": the group of FP7 projects working in the area of Advanced Computing and financed by the European Commission under ICT Call 10.

The main objective of the block review was to analyze, measure and maximize the potential and actual impact of the projects in terms of exploitation. Each project went through an autonomous review meeting, with a common allprojects workshop on impact and exploitation held on Wednesday, May 14. The P-SOCRATES review meeting focused on the achievements in the first phase of the project, which led to the successful reaching of the project first milestone. The project exploitation views were also presented in the Wednesday workshop, in a session on real-time and reliability.

The P-SOCRATES project will research and develop new techniques for exploiting the massively parallel computation capabilities of nextgeneration many-core embedded platforms in a predictable way. These platforms are well positioned for intercepting the increasingly convergence of High-Performance Computing (HPC) and Embedded Computing (EC) domains need for predictable high-performance, allowing HPC and EC applications to be executed on efficient and powerful heterogeneous architectures integrating general-purpose processors with manycore computing fabrics.

P-SOCRATES is tackling this important challenge by merging leading research groups from the HPC and EC communities. The time-criticality and parallelization challenges common to both areas are addressed by proposing an integrated framework for executing workload-intensive applications with real-time requirements on top of nextgeneration commercial-off-the-shelf (COTS) platforms based on many-core accelerated architectures. The project is investigating new HPC techniques that fulfil real-time requirements: the main sources of indeterminism are identified, and efficient mapping and scheduling algorithms will be proposeded, along with the associated timing and schedulability analysis, to guarantee the real-time and performance requirements of the applications.

The project partners include as research institutions, besides CISTER/INESC-TEC, the Barcelona Supercomputing Centre (Spain), the University of Modena (Italy) and the Swiss Federal Institute of Technology Zurich (Switzerland). The industrial partners of the project include ATOS (Spain) and the SMEs Evidence (Italy) and Active Technologies (Italy). The project partners are supported by an industrial advisory board, which includes well-known multi-national companies including Airbus, IBM, and Honeywell.

Besides overall coordination and technical management, CISTER/INESC-TEC is also deeply involved in the parallelism to real-time activity, leading in particular the Timing and Schedulability analysis work package.

# Program Co-Chair of WFCS2014

CISTER/INESC-TEC researcher Eduardo Tovar was program co-chair of the 10th IEEE Workshop on Factory Communication Systems (WFCS) held on May 5-7 in Toulouse, France. The WFCS workshop is the largest IEEE technical event specially dedicated to industrial communication systems, which aims to provide a forum for researchers, practitioners and developers to review current trends in this area and to present and discuss new ideas and new research directions.

The 2014 program included two interesting keynotes, one on on-board networks in space systems by Olivier Notebaert, Airbus Defence and Space, France, and another one on the history of industrial communication systems over the last two decades (from Fieldbus to Automation cloud) by Peter Neumann, IFAK Magdeburg, Germany.

CISTER/INESC-TEC was the organizer of the 2000 edition in Porto (http://www.hurray.isep.ipp.pt/wfcs200 0/)

#### June

# Successful Project Review Meeting of European Project Encourage

The 3rd review meeting of ENCOURAGE project, which involves the development of a reference platform for smart grids, was held in Barcelona. The review centered on the system's middleware, implemented mainly by CISTER, and on the demonstrator deployed in Terrassa University, which monitors the campus energy consumption, produces detailed report on energy usage, and publishes real-time data on Twitter regarding how

users use appliances and consume energy. This latter feature implements an educative competitive game between the responsible parties for the different rooms the campus is divided into.

# Arrowhead multi-workpackage meeting

From the 9th to 12th of June Luis Lino participated on the Arrowhead Multi-Workpackage Meeting, which was held in Stavanger, Norway. During this meeting all pilot-related tasks demonstrated their main achievements by showing around 15 different demo

installations running partially on existing Arrowhead technologies.

In this meeting CISTER/INESC-TEC showed a prototype of a system which applies the flex-offer concept (a kind of energy demand-response) on the control of a legacy devices, whose operation can be controlled by smart grid applications. These legacy devices can be almost any kind of electric devices which have some flexibility on the amount of energy to be consumed and on the time when that energy is consumed. Examples of these devices are washing machines, electric heater, heat-pumps, air-conditioning, etc.

The software, implemented by César Teixeira in close cooperation with Danish partners, can now be used, with the minor adaptations, on any other Arrowhead pilot that wishes to implement the flex-offer concept.

Arrowhead belongs to the first group of very large Artemis AIPP projects. It has an overall budget of around 90 million Euros, involving most European countries. Besides ISEP (through CISTER/INESC-TEC), the Arrowhead project involves key European industrial players such as Acciona (SP), Airbus Operations (FR), FIAT (IT), Ford (UK), Honeywell (CZ), INDRA (SP), Infineon (AT), NXP (FR), Schneider Electric (FR), STMicroelectronics (IT), and Thales (FR).

The Arrowhead project addresses cooperative automation and is enabled by the technology developed around the Internet of Things and Service Oriented Architectures. The project will provide a technical framework adapted to such systems. Implementation and evaluation will be through real deployments in various applicative domains: electro-mobility; smart buildings; infrastructures and smart

cities; industrial production; energy production and energy virtual market.

# CISTER wins fair-play team medal

Like in previous years, INESC-TEC organized last May a football tournament gathering all its researchers. CISTER/INESC-TEC researchers have been participating in this initiative since 2012.

In this year's tournament, CISTER/INESC-TEC's team - Borislav Nikolic, Christos Chrysoulas, Patrick Yomsi, João Loureiro, Hamza Ijaz, Paulo Carvalho, Hazem Ali, Raghuraman Rangarajan, Miguel Pinho and Daniel Moreira - joined the team of HasLab, another autonomous research unit associated to INESC-TEC, which was composed of Francisco Maia, Ricardo Gonçalves, Francisco Cruz, João Paulo, Tiago Jorge and Paulo Jesus. This year 8 teams attended the matches to compete for the title of Best Team of the 14th INESC-TEC Football Tournament 2014.

Although CISTER/HASLab didn't reach the title, the team was elected by the other football teams as the Fair-Play Team being awarded the respective medal. CISTER/INESC-TEC had already taken home such a medal in the 12th edition of INESC's football tournament.

## EMC2 kickoff meeting

Eduardo Tovar and Pedro Souto participated in the kick-off meeting of subtask 8.2, Hybrid Avionics Integrated Architecture, of the EMC2 Artemis Project, that took place at Airbus Group premises in Munich on 27<sup>th</sup> June. In this meeting the Airbus partners presented an overview of the demonstrator and this was followed by a discussion on

how the contributions of other partners might be integrated in that demonstrator.

EMC2 (Embedded multi-core systems for mixed criticality applications in dynamic and changeable real-time environments, JU grant nr. 621429) aims to develop an innovative, sustainable service-oriented architecture for mixed criticality

applications in dynamic and changeable real-time environments, helping the European Embedded Systems industry to maintain its leading edge position. EMC2 is a project of 97 partners of embedded industry and research from 19 European countries and Israel with an effort of about 800 person years and a total budget of about 100 million Euro.

#### July

## Management Meeting of the TACLe COST Action

Konstantinos Bletsas represented Portugal at the TACLe ("Timing Analysis at the Code Level") COST Action Management Committee meeting in Madrid, Spain on Monday, 7th July. As Portugal's representative, CISTER is to "channel"/represent research interest in this area from Portuguese institutions.

This management meeting was mainly dedicated to budget allocation in preparation of the upcoming project year as well as to follow-up on the project-sponsored summer school. The TACLe meeting was held jointly with the main event for Worst Case Execution Time Analysis, the WCET 2014 workshop.

COST Actions are designed to create networks of researchers in Europe around a particular topic. In this particular case, it concerns code-level timing analysis and brings together researchers from key research organizations in Europe, like the Mälardalen University, Sweden, University of York, UK, or University of Saarbrücken, Germany.

## Another PhD defense which received the highest distinction

CISTER/INESC-TEC PhD student

Muhammad Ali Awan has successfully

defended his PhD dissertation titled

"Energy and Temperature Aware RealTime Systems" in University of Porto

under the supervision of Dr. Stefan M.

Petters. Ali was enrolled in a doctoral

program in electrical and computer

engineering (PDEEC) jointly taught by

CISTER/INESC-TEC and FEUP. It is the

third PhD defense from CISTER in 2014

and also the third one to receive the

highest distinction!

The dissertation attempts to provide energy efficient solutions and techniques to cope with the current trends in modern embedded computing systems, while closing the gap between theoretical research and practice. In particular, it focuses on operating system-level power management and exploits the available sleep states to improve on energy efficiency while mainly concentrating on leakage power dissipation. Various aspects of the system (CPU, I/O devices, thermal management etc.) have been explored for a large range of hardware platforms. The proposed solutions have lower online complexity and consider more realistic power models when compared

to the state-of-the-art approaches. Outcomes of this research have been published in many reputed international conferences such as ECRTS, RTAS, RTCSA, RTNS, SIES and ICESS. In addition to this, four more works are under submission in renowned journals.

The president of the jury was Professor Jose Alfredo Ribeiro da Silva Matos, director of Department of Electrical and Computer Engineering of the University of Porto. The two "local" reviewers were the Associate Professor Luis Miguel Pinho Almeida and the Assistant Professor Mario Jorge Rodrigues de Sousa from the Department of Electrical and Computer Engineering, also from the University of Porto, and the two "external" reviewers were the Professor Gerhard Fohler, director of Real-Time Systems group at Technische Universitat Kaiserslautern, Germany and the Associate Professor Marko Bertogna from Dipartimento di Scienze Fisiche, Informatiche e Matematiche, Universita di Modena e Reggio Eimilia, Italy. These external members are highly respected researchers in the field of Real-Time Systems.

Last but not least, Ali is now joining CISTER/INESC-TEC as a PostDoc researcher!

#### One more successful PhD defense

CISTER/INESC-TEC PhD student Dakshina Dasari has successfully defended her PhD thesis entitled "Timing Analysis of Real-Time Systems Considering the Contention on the Shared Interconnection Network in Multicores". Dakshina received her PhD with distinction from the University of Porto where she was enrolled in the PhD program jointly taught by CISTER/INESC-TEC and FEUP.

In her work Dakshina has studied multiple aspects of the contention problem for shared resources in multicore settings. A particular attention was given to the contention for a single shared memory bus and the potential impact of sharing that resource on the timing behavior of the applications. She has also studied other shared resources like the memory controller and the network-on-chip in modern many-core architectures. She has contributed significantly to that research domain and has developed a set of methods to augment the state-of-the-art worstcase execution time analysis techniques with the extra delay induced by these shared resources.

Dakshina has achieved solid performance throughout the four years of her PhD, with a total of four papers published in international conferences and one paper published in a renowned journal (and another one still under submission). The main opponents were Prof. Daniel Mossé from the University of Pittsburgh, (USA) and Prof. Thomas Nolte from Mälardalen University (MDH), Västerås (Sweden), both highly respected authorities in the field.

#### September

## CISTER visited by representatives of Embraer

On September 5th, CISTER was visited by representatives of Embraer, one of

the world's leading aircraft manufacturers with its headquarters in Brazil. CISTER seized the opportunity offered by this visit to organize a workshop day during which CISTER gave an overview of the projects and international efforts in which the team is involved.

## 2nd CISTER Industrial workshop: CiWork 2014

CISTER has organized and hosted the 2nd Industrial workshop on Real-time and Embedded Systems CiWork 2014, on September 26th.

### CiWork2014

CiWork 2014 gathered together around 40 industry representatives and researchers to discuss the most recent advances and innovations in the area of RTES. Being an industrial workshop the focus was on the presentations by companies which presented their views and needs and case studies.

This year's edition had two keynotes, one on European Opportunities in RTES (by FCT/GPPQ), and another on Regional Opportunities for industry-academia partnerships and the main regional strategic drivers by CCDR-N. Besides the two keynotes, there was a special focus on smart Cities with a round table lead by Câmara Municipal do Porto (department of Innovation) with the participation of Freedom Grow, Inova+, Associação Porto Digital and CISTER.

During the day several companies presented their case studies, methodologies, tools and industrial challenges in the domain of aerospace (GMV), power lines automation (EFACEC) factory automation (Critical Manufacturing), smart cities (ISA) and inovation management (Inova+).

The forum also served to create and foster synergies between industry and academia.

# CISTER hosted another distinguished seminar in September from Prof. Frank Mueller

Professor Frank Mueller (mueller@cs.ncsu.edu) visited CISTER and delivered a talk on "Predictability for Uni- and Multi-Core Real-Time/Cyber-Physical Systems" in order to: (1) highlight challenges and contributions in worst-case execution time analysis for real-time system considering architectural changes over time and (2) discuss future trends and open research problems.

Frank Mueller is a Professor in Computer Science and a member of multiple research centers at North Carolina State University. Previously, he held positions at Lawrence Livermore National Laboratory and Humboldt University Berlin, Germany. He received his PhD from Florida State University in 1994. He has published papers in the areas of parallel and distributed systems, embedded and real-time systems and compilers. He is a member of ACM SIGPLAN, ACM SIGBED and a senior member of the ACM and IEEE Computer Societies as well as an ACM Distinguished Scientist. He is a recipient of an NSF Career Award, an IBM Faculty Award, a Google Research Award and a Fellowship from the Humboldt Foundation.

## Final results of the BIC students (interns) at CISTER

Three pairs of enthusiastic BIC students from ISEP and FEUP joined CISTER for a three months internship program. During this time frame, they contributed to a set of very challenging projects (recalled below) under the supervision of CISTER researchers.

The presentation of their remarkable results is available at: www.cister.isep.ipp.pt/events/871/

#### Project 1: Sensing in motion: by Marco Rodrigues (ISEP) and Miguel Sandim (FEUP) oriented by Raghuraman Rangarajan and Vikram Gupta

Real-time environment monitoring is required to quickly address issues of pollution of noise, air, water and land. This is especially important in an urban scenario for situational awareness and improved decision making. Current air pollutant sensors are in fixed locations and away from critical places. The aim of this project is to make a modular UV-based system capable of autonomously taking environmental measurements at different localities and transmit this data in real-time.

#### Project 2: Vision feedback to control 3D motion: by Dalila Lima (FEUP) and Nuno Almeida (ISEP) oriented by Filipe Pacheco and Shashank Gaur

Quadcopters provide easy and affordable 3D movement capabilities and enable new robotic tasks. However controlling the position in space of a device with adequate accuracy is a challenge. In this project computer vision is used to provide real-time position feedback and enable simple control in the 3D space of the quadcopter. The target application is an plotter-like demonstration where the quadcopter can draw paths on a vertical wall without human assistance.

# Project 3: Tele-presence robot: by João Pacheco (ISEP) and Paula Fortuna (FEUP) oriented by Pedro Souto and Ricardo Severino

Conventional video-conference systems although very useful allow for limited interaction. This project will combine a video-conference system with a wifibot to allow for a more interactive experience. Its goal being to allow a user to roam around a remote place and interact with remote users via a video-conference system, e.g. to remotely assist in lab work.

#### October

#### CISTER-lead European project P-SOCRATES meets in Porto

On September 30th/October 1st, the partners of the European Project P-SOCRATES gathered at CISTER, for two days of intensive technical work. This included in-depth discussions of the scientific and technical work being carried in the project work packages, but important, the specification of the holistic system model and software stack, which will be presented for the 2nd milestone of the project, in the first quarter of 2015. The partners also evaluated the detailed feedback received by the commission on the

contents of the first review, which provided very positive remarks on the work being developed, confirming the relevance of the foreseen objectives, as well as stressing the capability and importance of innovation and exploitation.

The P-SOCRATES project is researching and developing new techniques for exploiting the massively parallel computation capabilities of next-generation many-core embedded platforms in a predictable way. These platforms are well positioned for intercepting the increasingly convergence of High-Performance Computing (HPC) and Embedded

Computing (EC) domains need for predictable high-performance, allowing HPC and EC applications to be executed on efficient and powerful heterogeneous architectures integrating general-purpose processors with many-core computing fabrics.