Nuno Alexandre Magalhães Pereira

# A Framework for the Timing Analysis of Ethernet-based Factory-floor Networks

### A Framework for the Timing Analysis of Ethernet-based Factory-floor Networks

by

Nuno Alexandre Magalhães Pereira

A thesis submitted in partial fulfilment of the requirements for the degree of

Master of Science

Department of Informatics

University of Minho

December 2004

Thesis Supervision:

Dr. Eduardo Manuel de Médicis Tovar

Computer Engineering Department of the

Polytechnic Institute of Porto

Thesis co-Supervision:

Dr. Paulo Martins de Carvalho

Informatics Department of the

University of Minho

#### **UNIVERSITY OF MINHO**

#### **ABSTRACT**

### A FRAMEWORK FOR THE TIMING ANALYSIS OF ETHERNET-BASED FACTORY-FLOOR NETWORKS

by Nuno Alexandre Magalhães Pereira

Throughout the years, researchers have developed and applied a considerable range of theory to the validation of factory-floor distributed real-time systems. Nowadays, some of those systems are based on Ethernet technologies. In fact, a number of characteristics are boosting the eagerness of extending Ethernet to also cover factory-floor distributed real-time applications. Full-duplex links, non-blocking and priority-based switching, bandwidth availability, just to mention a few, are characteristics upon which that eagerness is building up.

In the past few years, it is particularly significant the considerable amount of work that has been devoted to the timing analysis of Ethernet-based technologies. It happens, however, that the majority of those works are restricted to the analysis of subsets of the overall computing and communication system, thus without addressing the system as a whole. In fact, Ethernet technology, by itself, does not include features above the lower layers of the communication stack. Where are the higher layers that permit building real industrial applications? And, taking for free that they are available, what is the impact of those protocols, mechanisms and application models on the overall performance of Ethernet-based distributed factory-floor applications? This dissertation attempts to pave the way towards providing some reasonable answers to these issues.

To this end, a few analysis approaches are explored with the purpose of setting a framework for developing tools suitable to extract temporal properties of Commercial-Off-The-Shelf (COTS), Ethernet-based factory-floor communication systems. The particular case of Ethernet/IP is taken into the research work.

Two models, enabling finding end-to-end response times in Ethernet/IP based distributed systems are provided. The first model is an analytical model, built upon traditional real-time response time analysis, considering a number of worst-case assumptions to derive the end-to-end response time bounds. The second model is a discrete-event simulation model, providing an adequate solution to understand and analyse the timing behaviour of actual systems, also facilitating approaches for timeliness evaluation based on probabilistic measures of meeting deadlines. This may become relevant since modern factory-floor systems tend to be more flexible and adaptive in their nature. Additionally, results from applying both models are presented, and a discussion of the two is provided.

#### UNIVERSIDADE DO MINHO

#### **RESUMO**

### ABORDAGENS À ANÁLISE TEMPORAL DE REDES BASEADAS EM ETHERNET PARA AMBIENTES INDUSTRIAIS

por Nuno Alexandre Magalhães Pereira

Ao longo dos anos, diversos investigadores construíram e aplicaram uma quantidade considerável de teoria à validação de sistemas tempo-real distribuídos, para ambientes industriais. Actualmente, alguns destes sistemas são baseados em tecnologias de comunicação Ethernet. Na realidade, existe um conjunto de características que estão a aumentar a veemência para colocar tecnologias de comunicação baseadas em Ethernet em ambientes industriais. Características como ligações *full-duplex*, comutação não bloqueante e baseada em prioridades são apenas alguns exemplos que justificam tal veemência.

É particularmente significante a quantidade considerável de trabalho desenvolvido nos últimos anos dedicado à análise temporal de tecnologias baseadas em Ethernet. No entanto, acontece que a larga maioria destes trabalhos, limitam-se à análise de subconjuntos do sistema de computação e comunicação, não considerando portanto uma visão sistémica. De facto, a tecnologia Ethernet, por si só, não inclui funcionalidades acima das camadas mais baixas da pilha protocolar de comunicações. Onde se encontram então as camadas superiores, que permitem construir aplicações concretas? Adicionalmente, assumindo que estas se encontram facilmente disponíveis, qual é o impacto, a um nível sistémico, da introdução desses protocolos, mecanismos e aplicações no desempenho das aplicações distribuídas baseadas em Ethernet? Esta dissertação empreende esforços no sentido de fornecer algumas respostas razoáveis a estas questões.

Para este fim, algumas abordagens para análise temporal são exploradas com o intuito de formar um enquadramento apropriado para o desenvolvimento de ferramentas e métodos adequados à extração das propriedades temporais de redes Ethernet para ambientes industriais, baseadas em componentes disponíveis comercialmente. Neste trabalho é tomado o caso particular de sistemas Ethernet/IP distribuídos.

Foram concebidos dois modelos que permitem encontrar o atraso ponto-a-ponto em sistemas Ethernet/IP distribuídos. O primeiro é um modelo analítico, assente em conceitos tipicamente utilizados em análises de sistemas computacionais tempo-real, que consideram um conjunto de suposições sobre os cenários mais pessimistas de utilização dos recursos em causa, para derivar os limites máximos do atraso ponto-a-ponto. O segundo modelo é baseado em simulação discreta de eventos, possibilitando uma solução adequada para a compreensão e análise do comportamento temporal de sistemas concretos. Este segundo modelo facilita também a abordagem do problema de uma forma não determinística, facultando medidas probabilísticas do cumprimento dos atrasos máximos impostos ao sistema. Tais resultados tornam-se relevantes à luz da natureza mais adaptativa e flexível dos sistemas industriais modernos. Adicionalmente, são apresentados resultados obtidos a partir dos dois modelos, juntamente com uma discussão sobre ambos.

### CONTENTS

| 1 | C   | OVERVIEW                                                            | 1  |

|---|-----|---------------------------------------------------------------------|----|

|   | 1.1 | Introduction                                                        | 1  |

|   | 1.2 | RESEARCH CONTEXT                                                    | 2  |

|   | 1.3 | HYPOTHESIS AND OBJECTIVES                                           | 3  |

|   | 1.4 | OUTLINE OF THE DISSERTATION                                         | 3  |

|   | 1.5 | RESEARCH CONTRIBUTIONS                                              | 3  |

| 2 | Т   | FECHNOLOGICAL CONTEXT: COMMUNICATION INFRASTRUCTURE                 | 5  |

|   | 2.1 | Introduction                                                        | 5  |

|   | 2.2 | ETHERNET REVIEW                                                     | 6  |

|   | 2.3 | ETHERNET/IP (EIP)                                                   | 9  |

|   | 2   | 2.3.1 General Aspects                                               |    |

|   |     | 2.3.2 CIP Messaging                                                 | 11 |

|   |     | 2.3.3 Producer/Distributor/Consumer Model                           |    |

|   | _   | 2.3.4 Ethernet/IP Devices                                           |    |

|   |     | 2.3.6 Assumptions                                                   |    |

|   | 2.4 | SUMMARY                                                             | 15 |

| 3 | Т   | TECHNOLOGICAL CONTEXT: SIMULATION SOFTWARE                          | 17 |

|   | 3.1 | Introduction                                                        | 17 |

|   | 3.2 | SIMULATION LANGUAGES                                                | 18 |

|   | 3.3 | NETWORK SIMULATION PACKAGES                                         | 19 |

|   | 3.4 | A FEW MORE DETAILS ON OMNET++                                       | 21 |

|   | 3.5 | SUMMARY                                                             | 23 |

| 4 | A   | APPROACHES FOR TIMELINESS ANALYSIS                                  | 25 |

|   | 4.1 | Introduction                                                        | 25 |

|   | 4.2 | BASIC CONCEPTS OF REAL-TIME SYSTEMS                                 | 25 |

|   | 4   | 4.2.1 Characterization of Tasks                                     |    |

|   |     | 4.2.2 Scheduling Tasks in Real-time Systems                         |    |

|   |     | 4.2.3 Priority Assignment Schemes                                   |    |

|   |     | ANALYTICAL-BASED TIMING ANALYSIS                                    |    |

|   |     | 4.3.1 Utilization-Based Tests                                       |    |

|   |     | 4.3.3 From Task to Message Schedulability Analysis                  |    |

|   | 4.4 |                                                                     |    |

|   | 4   | 4.4.1 Meaningful Results from Simulation Output Data                | 36 |

|   | 4   | 4.4.2 Statistical Ground for the Analysis of Simulation Output Data | 37 |

|   |     | 4.4.3 Non-Terminating Simulations                                   |    |

|   |     | 4.4.4 Other Measures of Performance                                 |    |

|   | 4.5 | Summary                                                             | 42 |

| 5  | WOF            | RST-CASE BASED ANALYTICAL MODEL                                   | 43  |

|----|----------------|-------------------------------------------------------------------|-----|

|    | 5.1 IN         | TRODUCTION                                                        | 43  |

|    | 5.2 EN         | D-TO-END LATENCY FORMULATION                                      | 43  |

|    | 5.3 LA         | TENCY INTRODUCED BY THE EA ( $Qea_{M}$ )                          | 44  |

|    | 5.4 LA         | TENCY INTRODUCED BY THE BACKPLANE ( $QB_{\scriptscriptstyle M}$ ) | 45  |

|    | 5.5 LA         | TENCY INTRODUCED BY THE SWITCH ( $Lt^{SW}$ )                      | 46  |

|    | 5.6 Nu         | IMERICAL EXAMPLE                                                  | 47  |

|    | 5.7 Su         | MMARY                                                             | 48  |

| 6  | SIMU           | JLATION BASED TIMING ANALYSIS OF EIP NETWORKS                     | 49  |

|    | 6.1 IN         | FRODUCTION                                                        | 49  |

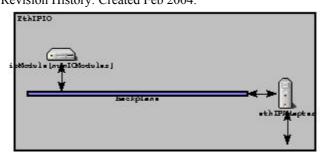

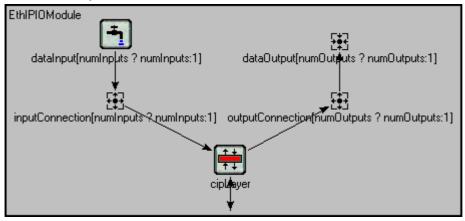

|    | 6.2 TH         | E REMOTE IO NODE                                                  | 49  |

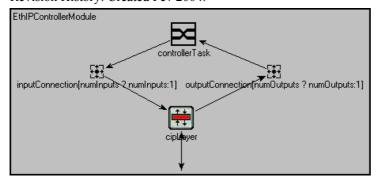

|    | 6.3 TH         | E CONTROLLER NODE                                                 | 53  |

|    | 6.4 TH         | E SWITCH NODE                                                     | 54  |

|    | 6.5 Ex         | AMPLE SCENARIO                                                    | 55  |

|    | 6.5.1          | Statistical Results of the Simulation                             | 57  |

|    | 6.6 SU         | MMARY                                                             |     |

| 7  | CON            | CLUSIONS AND FUTURE WORK                                          | 61  |

|    | 7.1 Su         | MMARY AND CONCLUSIONS                                             | 61  |

|    | 7.2 Fu         | ture Work                                                         | 64  |

|    | 7.2.1          | Fine-tuning and Thorough Validation of the Models                 | 64  |

|    | 7.2.2          | =                                                                 |     |

|    | 7.2.3          |                                                                   |     |

| Di | 7.2.4          | Different Measures of Performance in Simulation Studies           |     |

|    |                | V                                                                 | *** |

| -  |                | 1                                                                 |     |

|    |                |                                                                   |     |

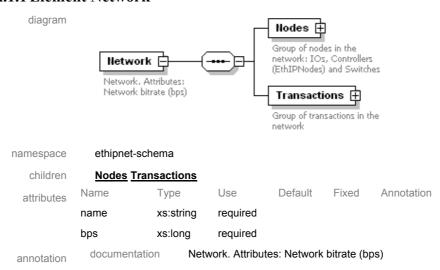

| Al |                | ( A                                                               |     |

|    |                | TWORK DEFINITION SCHEMA DOCUMENTATION                             |     |

| Al | PPENDIX        | ( B                                                               | 91  |

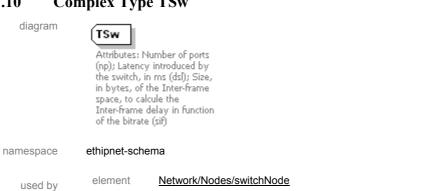

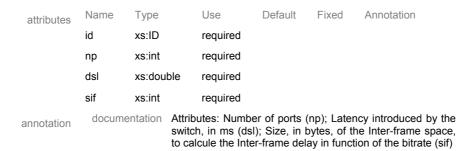

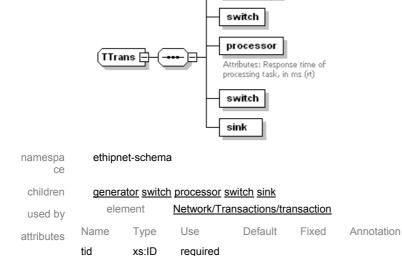

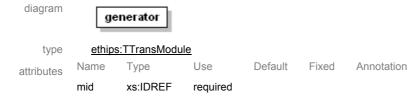

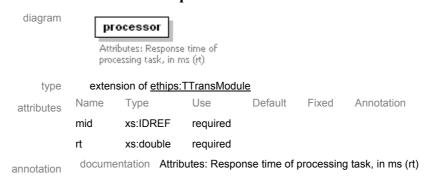

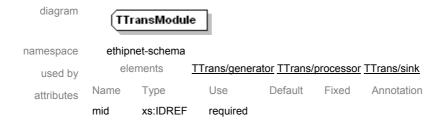

|    | B.1 SI         | MULATION MODEL DOCUMENTATION                                      | 91  |

|    | B.1.1          |                                                                   |     |

|    | B.1.2<br>B.1.3 | T                                                                 |     |

|    | B.1.3<br>B.1.4 |                                                                   |     |

|    | B.1.5          | 0                                                                 |     |

### LIST OF FIGURES

| FIGURE 1. TYPICAL MODERN SWITCH INTERNALS                                    | 7  |

|------------------------------------------------------------------------------|----|

| Figure 2. Ethernet MAC header with 802.1Q tagging                            | 8  |

| FIGURE 3. CIP COMMON LAYERING OVER DIFFERENT NETWORKS                        | 10 |

| Figure 4. CIP and Ethernet in the TCP/IP layering model                      | 11 |

| FIGURE 5. SOURCE/DESTINATION MODEL ILLUSTRATION                              | 12 |

| Figure 6. Producer/distributor/consumer model illustration                   | 12 |

| Figure 7. EIP basic nodes                                                    | 13 |

| Figure 8. EIP end-to-end transaction                                         | 14 |

| FIGURE 9. OMNET++ MODULE HIERARCHY                                           | 22 |

| FIGURE 10. OMNET++ GATES AND CONNECTIONS                                     | 22 |

| Figure 11. Task attributes                                                   | 27 |

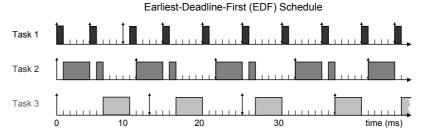

| FIGURE 12. RM AND EDF SCHEDULE EXAMPLES ON 1 PROCESSOR                       | 29 |

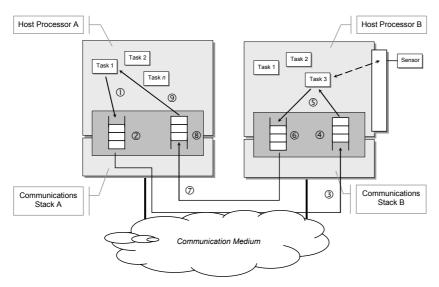

| FIGURE 13. END-TO-END COMMUNICATION DELAY                                    | 34 |

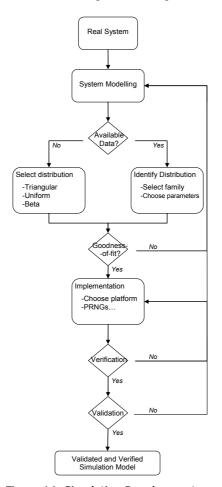

| FIGURE 14. SIMULATION DEVELOPMENT                                            | 35 |

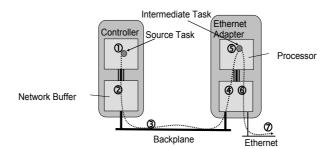

| FIGURE 15. CONTROLLER: MESSAGE DELAY COMPONENTS                              | 45 |

| FIGURE 16. BACKPLANE MEDIUM ACCESS CONTROL SCHEME                            | 45 |

| FIGURE 17. EXAMPLE SCENARIO                                                  | 47 |

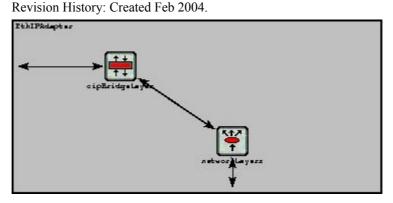

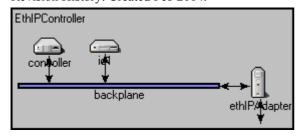

| FIGURE 18. EIP SIMULATION MODEL HIERARCHY IN OMNET++                         | 49 |

| FIGURE 19. BACKPLANE NED DEFINITION.                                         | 50 |

| FIGURE 20. ETHIPADAPTER NED DEFINITION.                                      | 51 |

| FIGURE 21. OMNET++ ETHIPIOMODULE COMPOSITION.                                | 52 |

| FIGURE 22. IOCONNECTION CLASS MESSAGE HANDLER C++ CODE                       | 52 |

| FIGURE 23. OMNET++ ETHIPIOMODULE NED CODE FOR PARAMETER CONFIGURATION        | 53 |

| FIGURE 24. ETHIPIOMODULE PARAMETER CONFIGURATION THROUGH INITIALIZATION FILE | 53 |

| FIGURE 25. OMNET++ CONTROLLER MODULE COMPOSITION                             | 54 |

| FIGURE 26. ETHERNET SWITCH NED DEFINITION.                                   | 54 |

| FIGURE 27. ETHERNET CHANNEL DEFINITION IN OMNET++                            | 55 |

| Figure 28. Simulated system depiction.                                       | 56 |

### LIST OF TABLES

| TABLE 1. EXAMPLE TASK SET                                                       | 29 |

|---------------------------------------------------------------------------------|----|

| TABLE 2. ASSUMPTIONS FOR DEVICE PARAMETERS                                      | 4′ |

| TABLE 3. TRANSACTIONS RESPONSE TIME RESULTS                                     | 4  |

| Table 4. End-to-End transactions                                                | 50 |

| TABLE 5. INPUT CONNECTIONS                                                      | 5′ |

| TABLE 6. CONNECTIONS AT THE CONTROLLER                                          | 5′ |

| TABLE 7. OUTPUT CONNECTIONS                                                     | 5′ |

| TABLE 8. RESULTS OF SIMULATION OUTPUT USING REPLICATION/DELETION                | 5  |

| TABLE 9. ANALYTICAL MODEL RESULTS FOR PREVIOUSLY SIMULATED SCENARIO (FIGURE 28) | 62 |

| TARLE 10 COMPARISON OF SIMILIATION WITH ANALYTICAL MODEL DESLIETS               | 6' |

### LIST OF ACRONYMS

ARP Address Resolution Protocol

CAN Controller Area Network

CIP Control and Information Protocol

CORBA Common Object Request Broker Architecture

CoS Change-of-State

**COTS** Commercial-Of-The-Shelf

**CSMA/CD** Carrier Sense Multiple Access with Collision Detection

CTDMA Concurrent Time Domain Multiple Access

DCOM Distributed Component Object Model

**DEC** Digital Equipment Corporation

**EDF** Earliest Deadline First

EIP Ethernet/IP

**FPS** Fixed Priority Scheduling

ICMP Internet Control Message Protocol

**IEEE** Institute of Electrical and Electronics Engineers

IGMP Internet Group Management Protocol

IP Internet Protocol

IPC Inter-Process Communication

Java/RMI Java Remote Method Invocation

MAC Medium Access Control

MAP Manufacturing Automation Protocol

**NED** NEtwork Description

**OMNeT++** *Objective Modular Network Testbed in C++*

OPC OLE for Process Control

OSI Open Systems Interconnection

PRNG Pseudo-Random Number Generator

RARP Reverse Address Resolution Protocol

RIO Remote Input/Ouptut (IO)

**RM** Rate Monotonic

**RPI** Requested Packet Interval

**SNMP** Simple Network Management Protocol

TCP/IP The Internet protocol suite

TCP Transmission Control Protocol

UDP User Datagram Protocol

TDMA Time Division Multiple Access

WCET Worst-case Execution Time

**WWW** World Wide Web

### **ACKNOWLEDGMENTS**

First of all I want to thank my supervisor, Dr. Eduardo Tovar, for his guidance, advice, support, and for always being available for insightful and enjoyable conversations. I would also like to thank Dr. Paulo de Carvalho for taking interest in my work and for is understanding through the development process of this dissertation.

The work leading up to this thesis was done at the IPP-HURRAY! Research Group, at the School of Engineering of the Polytechnic Institute of Porto. Working at IPP-HURRAY! Has been very stimulating and instructive, and the atmosphere in the group has given rise to several interesting discussions and ideas, on topics related to my work at different levels and otherwise interesting topics. The pleasant research atmosphere at the group is of course a product of all the members of the group. My appreciation to all of you. To Berta Batista, Dr. Mário Alves, Dr. Luís Ferreira, Filipe Pacheco and many thanks to Dr. Miguel Pinho.

Thanks also to Pedro Fortuna, for several interesting discussions and ideas on everything concerning computers.

My gratitude to my Parents, José and Odete, for all the support. And, finally to adorable Eduarda, for standing by me and making life more pleasant.

### Chapter 1

### **OVERVIEW**

### 1.1 Introduction

Today, high innovation-rate companies already make more than 60% of their profit on products less than two years old. Actually, in many industries, product lifecycles are halving every five years [1]. It is becoming less and less viable to sell from stock and have high value finished goods tying up capital. To satisfy the needs from a variety of clients, manufacturing companies are increasingly focusing on agility of operation. To serve these needs, rapid sequencing, configuration and reconfiguration of manufacturing equipment are essential.

In such context, organisational and supply chain agility are becoming key requirements for manufacturing in any sector. From order receipt, through manufacturing and product delivery, an enormous number of variants that need to be handled are introduced, turning information management a vital strategic asset for any manufacturing company today.

The factory-floor, being a central component of every manufacturing enterprise, is the starting point for greater information connectivity. Computer-based factory-floor controls for manufacturing machinery, materials handling systems and related equipment generate a wealth of information about productivity, product design, quality and delivery. Thus, factory-floor networking arises as a prominent building-block for unleashing this information in a cost-effective manner [2].

In a typical automated factory-floor, there will be a controlled system, for example robots or assembling stations and a controlling system that can include the computers and human interfaces that manage and coordinate the activities on the factory-floor. The controller system interacts with the controlled system based on the information available, collected from various sensors. It is imperative that the state of the controlled system, as perceived by the controlling system, is consistent with its actual state. Otherwise, the effects of the controlling systems' activities may lead to serious failures. Hence, periodic monitoring of the environment as well as *timely* processing of the sensed information is necessary. Noticeably, timely delivery support from the network is essential to have distributed automation applications in the factory-floor.

Consider, for example, a sub-system composed of a conveyer belt, where manufactured parts are carried after assembly. A robotic actuator is responsible for distributing the parts between several packaging stations. The information about where to deliver the parts is collected from another sub-system that gathers information about the available packaging stations. In such system, a timely coordination between the information collected from sensors that detect the parts on the conveyer belt, the packing sub-system and the robotic

actuator is essential for this system [3]. Failing to do so may result in the need for human intervention and possibly halting the production system.

A system where its correctness depends not only on the logical result of computation, but also on the time at which the results are produced is defined as a real-time computing system [4].

### 1.2 Research Context

The timeliness analysis of real-time systems is usually exploited in a framework dominated by the notion of absolute temporal guarantees. In those systems, computational and communication loads are presumed to be bounded and known, and the worst-case (at least believed to be) conditions are assumed. In this way, the problem of engineering distributed real-time systems, of which factory-floor distributed computing systems are a representative example, becomes a problem of devising the appropriate tools and methods to assure that all deadlines are met in all circumstances [5].

To this end there are generally three, usually alternative, approaches. The first consists of building a prototype of the system and perform extensive testing. Although this is conceptually a simple method, in practice, it is usually hindered by many difficulties. To build the prototype may take a considerable amount of resources and even once the prototype is built, it may be impossible to consider and analyse all possible interactions that affect the timing behaviour of the system.

Another option is to develop an analytical model of the worst-case timing behaviour of the system and draw conclusions based on the model. Much research has been done over the years to examine system behaviour based on several real-time system models. However, and for complex distributed systems, analytical models tend to be overwhelmed with simplifications that often lead to very pessimistic assumptions, and therefore to very pessimistic worst-case results. Even knowing that a number of existing techniques may potentially be used and adapted to reduce this pessimism level, the benefit may appear at the cost of adding rather complex abstractions, such as precedence relationships [6], event phasing [7, 8] and inheritance of time characteristics [9, 10]. These, unfortunately, may lead to intractable analytical models, thus making it further difficult to handle and reason the analytical abstractions.

To add on top of this, some characteristics of the system may not lend themselves to deterministic analysis techniques. For example, the arrival pattern of messages or communication times may not be completely deterministic and conversely can be characterised in a probabilistic manner. The emergence of "more complex" distributed systems, with a more flexible and adaptive nature creates the eagerness to approach the timeliness evaluation problem in a different way: instead of using a guaranteed approach, why not tackling the problem by trying to find a probabilistic measure of meeting deadlines?

It is in this context that simulation (the third alternative for the timeliness evaluation of a system) can emerge as an adequate solution to tackle the problem of engineering complex distributed real-time systems. On the other hand, the relatively recent advent of fast and inexpensive computational power allows the approach of trying to model the system as faithfully as possible, and then use simulation to obtain accurate characteristics. The use of

simulation models that mirror the behaviour of the system under analysis may provide a reasonable framework for the timeliness evaluation of such distributed real-time systems. In this dissertation, such approach is applied to a specific COTS technology, Ethernet/IP [11].

### 1.3 Hypothesis and Objectives

This dissertation explores the development of tools suitable to extract temporal properties of Ethernet-based factory-floor communication systems. This problem can be tackled using different and possibly inter-linked methods.

A major question to be answered is to what extent simulation can be used to extract useful timeliness results about the modelled systems.

### 1.4 Outline of the Dissertation

This dissertation will proceed by firstly presenting the technological context behind it. Details of the factory-floor technology chosen to support the analysis of an overall communication infrastructure is presented (Chapter 2). Then, in Chapter 3, some of the extant simulation tools for the development of network simulation models are surveyed.

In Chapter 4, the basis for the timeliness approaches followed is presented. Some introductory real-time systems concepts are laid out to introduce the foundations of traditional response time analysis, also applicable to the analysis of distributed systems. Then, the statistical grounds for adequately extracting performance measures from simulation output data are overviewed.

The next two chapters present the models developed for the timeliness analysis of Ethernet/IP-based distributed systems. These models are based on the two approaches introduced in Chapter 4. Therefore, in Chapter 5, a worst-case analytical model is proposed. In Chapter 6, a simulation model for Ethernet/IP, using a specific simulation tool is proposed.

The closing chapter (Chapter 7) of the dissertation presents a brief summary and conclusions of this work, along with a discussion on the results obtained by both models developed. It also introduces a number of topics for future research. Among these topics, the advancement of some options for the extraction of other measures of performance from simulation models, assumes a particular relevance.

### 1.5 Research Contributions

The main contributions of this dissertation are the following:

- an analytical model for EIP distributed systems, providing the worst-case end-toend response time of distributed transactions [12];

- a simulation model for EIP distributed systems [13];

- approach to a framework for extracting measures of performance from simulation models, including performance measures other than means [14];

- a framework for the extraction of overall temporal properties of COTS factoryfloor communication systems through the combination of different, but potentially integrated, types of analysis [15].

### Chapter 2

### TECHNOLOGICAL CONTEXT: COMMUNICATION INFRASTRUCTURE

### 2.1 Introduction

Over the last decade, factory-floor networking has evolved from relatively passive and isolated data collection or reporting roles to feedback control and diagnostics applications, integrated with enterprise-wide information systems. Modern industrial systems must be able to exploit commercial information technologies, including Commercial-Off-The-Shelf (COTS) operating-systems; TCP/UDP/IP based applications and general purpose networks.

However, it is interesting to observe that the development of factory-floor networking has been far slower than the development of office networks. One of the reasons for this delay is related with the timing requirements found in factory-floor applications. To have precise control over the data-sampling task, a common solution used to be employing pointto-point wiring. While being a simple solution, it is important to note that traditional pointto-point wiring is very limited in the information it transmits or receives from the field, because only the process variable is communicated, without any diagnostic or health information. The first step towards an actual factory-floor networking environment was the fieldbus concept. Fieldbusses are a cost-saving solution (being cabling one of the major cost components in any factory-floor installation) that provides much more information and flexibility. Nevertheless, fieldbus technologies present some important drawbacks. The fieldbus market is a small one (when compared to the office network market), where the prices are fairly high and the technology development is rather slow. Conversely, the office network market is rapidly evolving, with enormous data throughput increases and price drops of equal magnitude. Particularly, the high-speed properties of Ethernet, its familiarity and low cost make it a potential candidate for factory-floor communications.

Ethernet was, until recently, generally known for exhibiting unstable performance (e.g. unbounded delay) under heavy load. However, advances in switched-Ethernet made Ethernet more predictable, and have increased the eagerness to introduce Ethernet-based technologies into the factory-floor [16, 17].

Still, there are obstacles to overcome. Indeed, a few research efforts on Ethernet technologies have been focusing on timeliness, trying to find solutions to issues such as bounded response time evaluation, optimal scheduling policies, switching topologies or clock synchronisation [18]. However, they essentially consider the timing characteristics at the Data Link Layer, meaning that an overall approach embracing a fully defined protocol stack is still lacking.

While until a couple of years ago a valid justification for this gap could eventually be the lack of technologies offering an overall ensemble of protocols and mechanisms [19], this justification cannot serve that purpose anymore. In fact, there are already some COTS solutions for Ethernet-based systems providing a fully-defined communication protocol stack. One of such solutions, based on encapsulation technologies, is Ethernet/IP (EIP), where IP stands for "Industrial Protocol".

In the next section some further details will be surveyed on Ethernet technologies, in particular those characteristics enabling its use to support real-time distributed systems. Then, Section 2.3 is devoted to describing the more important details related to Ethernet/IP technologies.

### 2.2 Ethernet Review

Ethernet is a set of network cabling and signalling specifications originally developed by Xerox, in the late 1970. It was called Ethernet after the *luminiferous ether* as a way of describing an essential feature of the system: the physical medium (i.e., a cable) carries bits to all stations, in a way analogous to the *luminiferous ether* that once was thought to propagate electromagnetic waves through space.

In 1980, Digital Equipment Corporation (DEC), Intel and Xerox began joint promotion of this baseband, Carrier Sense Multiple Access/Collision Detection (CSMA/CD) computer communications network over coaxial cabling, and published the "Blue Book Standard" for Ethernet Version 1. This standard was later enhanced, and in 1985 Ethernet Version 2 was released.

The Institute of Electrical and Electronics Engineer's (IEEE's) Project 802 then used Ethernet Version 2 as the basis for the 802.3 CSMA/CD network standards. The IEEE 802.3 standard is generally interchangeable with Ethernet Version 2, with the greatest difference being the construction of the network packet header. For the sake of precision, it is important to point out that, in the context of this document, 803.2 would be a more appropriate terminology than Ethernet, when referring to the family of CSMA/CD-based Medium Access Control (MAC) protocols.

A complete description of all Ethernet specifications is far outside the scope of this dissertation, and for further details the reader should refer to the IEEE 802.3 standard [20].

Without going into details, the general idea of the CSMA/CD MAC protocol can be described in the following way. When a station wants to transmit, it listens to the cable. If the cable is busy, the station waits until it goes idle. Otherwise, it transmits immediately. If two or more stations begin transmitting on an idle cable simultaneously, the messages will collide. All colliding stations then terminate their transmission, wait a random time, and repeat the whole process all over again [21].

In a heavily loaded (in terms of traffic volume) network, a station can experience an unbounded number of collisions and, therefore, the time to transmit a frame is also unbounded, justifying the argument of non-deterministic behaviour frequently utilised against the use of Ethernet for distributed control applications in the factory-floor. Determinism enables systems designers to accurately predict the worst-case transmission delay. Another requirement for factory-floor networks is high repeatability (or low jitter);

That is, the guarantee that a periodic message is transmitted successfully almost periodically. This requirement was also difficult to attain with former Ethernet-based technologies.

Developments in Ethernet technology have improved the determinism, repeatability and performance of Ethernet to a great extent. Next, a briefly survey some of those developments is made.

A major step toward deterministic and repeatable behaviour in Ethernet networks resides in the elimination of the random behaviour of CSMA/CD, by avoiding collisions in the network. This can be achieved by using specialised hardware at the heart of the communication infrastructure with an array of *ports* to which all the communicating devices are connected to. This specialised hardware, called *switching hubs*, *layer 2 switches* or simply *switches*, allow traffic to be relayed between any two ports. Current switch technology does this operation at very high speeds and introducing, and extremely low latency.

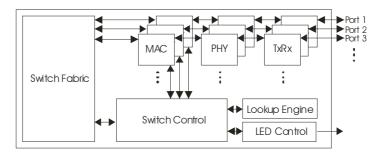

Figure 1. Typical modern switch internals

Most modern Ethernet switches (internals depicted in Figure 1) support full duplex operation, allowing simultaneous two-way transmission over point-to-point links. Since switches provide a separate collision domain for each port, using full-duplex communication, collisions do not exist at all.

Recent switches typically announce wire-speed and non-blocking operation. Wire-speed means that all ports of a switch can simultaneously transmit or receive at their full bit rates. This requires that the switch fabric can operate at a bit rate equalling to the aggregate speeds of all the ports. For example, 24 full-duplex ports operating at 200 Mbps (100 Mbps in each direction) implies a fabric switching at 4.8 Gbps (24×200 Mbps). A switch is non-blocking if it can forward a message to the destination port as long as that port is free, while a blocking switch may not be able to forward a message to a free port due to internal conflicts in the switch fabric.

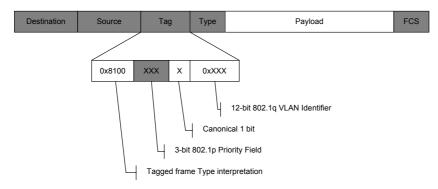

If traffic is sent to an output port at a higher rate than its capacity, packets must be queued. Queuing exists in any switch, regardless of whether it is full wire-speed or not, and the analysis of the queuing delay depends on knowledge on the input traffic pattern. To alleviate switch queuing problems, support for message prioritisation (IEEE 802.1p) was introduced. The standard specifies a layer 2 mechanism for giving mission-critical data preferential treatment over non-critical data [20, 22]. The concept, driven by the multimedia

industry, is based on priority tagging of packets and implementation of multiple queues to discriminate packets. For tagging purposes, IEEE 802.3q [20] defines an extra field for the Ethernet MAC called *Tag Control Info* (TCI), containing 3 priority bits, thus the standard defines 8 different levels of priority (Figure 2).

Figure 2. Ethernet MAC header with 802.1q tagging

Taking a closer look at Figure 2, it is possible to observe that the tag contains more than just priority bits. It also contains a 12-bit VLAN identifier. This field is used in advanced switches to allow logically separated networks - virtual LAN (IEEE 802.1q). VLANs permit configuring the switch so that its ports are subdivided into different broadcast groups, such that all packets received on one port of a group will only be transmitted to the ports on the same group, thus isolating broadcast traffic between logically separated networks (each group).

Several fault-tolerance mechanisms are available through spanning trees and port trunking. The Spanning Tree Protocol [20] can be used to provide redundant network paths, still protecting against network loops. Port Trunking establishes backbone links by treating multiple parallel links as a single network pipe. It also provides link redundancy, i.e., traffic on any failed link comprising a network trunk, automatically switches over to the other links in the trunk.

By itself, Ethernet only supports transmission of frames in a LAN. Ethernet lacks more complex features required for a fully functional LAN. Generally, Ethernet networks support one or more communication protocols that run on top of Ethernet and provide sophisticated data transfer and network management functions. It is the communication protocol that determines the level of functionality supported by the network. Protocols (such as AppleTalk, Inter-Process Communication (IPC) or Manufacturing Automation Protocol (MAP)) have been implemented over Ethernet. Of these, TCP/IP is the most popular, due to the emergence of the global *Internet*, including the *World Wide Web* (WWW). Although TCP/IP runs on physical media other than Ethernet, and Ethernet supports other communication protocols, the two have become increasingly linked.

Throughout the years, Ethernet has become a *de facto* standard, supporting many widely spread upper layer protocols like the TCP/IP stack, including the vast range of TCP/IP's stack application protocols such as FTP, HTTP or SNMP. This facilitates the use of Ethernet and allows easily integrating many COTS software components such as OLE for

Process Control (OPC), Microsoft Distributed Component Object Model (DCOM), Common Object Request Broker Architecture (CORBA), Java/Remote Method Invocation (RMI), and many others.

To summarise, today's Ethernet technology offers the following main interesting features for factory-floor networks:

- generous bandwidth (e.g. 10 Mbps, 100 Mbps, 1 Gbps, 10 Gbps);

- deterministic network access delay, due to switching principles and full-duplex links;

- priority handling (IEEE 802.1p), a basic support mechanism for real-time communication;

- broadcast traffic isolation and enhanced security through VLANS;

- reliability improved using Spanning Tree Protocol on redundant links;

- *de facto* standard supporting many widely spread upper protocol stacks.

### 2.3 Ethernet/IP (EIP)

### 2.3.1 General Aspects

Ethernet/IP (EIP), is a communication system suitable for use in industrial environments and time-critical applications [11]. It is an open industrial networking standard that takes advantage of COTS Ethernet communication chips and physical media, implementing a full suite of control, configuration and data collection services on top of an Ethernet network.

EIP makes use of an open protocol named Control and Information Protocol (CIP). CIP is an Application Layer protocol that implements a distributed object model. The CIP protocol specification [23] is quite extensive. Mainly, it defines the abstract *object modelling* used to describe the suite of communication services available, the externally visible behaviour of a CIP node and a common means by which information within a CIP-based network is exchanged. It also defines the *messaging protocol* used and the *communication objects* necessary to manage and provide run-time exchange of messages.

In addition, the CIP protocol specification also includes a fairly large collection of commonly used objects such as analogue Input/Output points, position sensor, AC/DC drive, etc, called the *General Object Library*. To avoid having devices of similar functionality from different vendors described with dissimilar object structures, devices of similar functionality are grouped into *device types*, with an associated *device profile* that describes the objects (some required, some optional) and the behaviour associated with that particular type of device.

The CIP protocol specification also made provisions for configuring the devices defining an *Electronic Data Sheet* (EDS) format to provide a full description of all configurable information of a device.

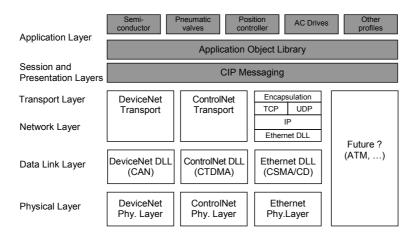

CIP is implemented on top of several different networks: DeviceNet [24], ControlNet [25] and Ethernet, allowing transparent application-level interoperability between factory-floor equipment. Figure 3 depicts CIP's common layering on top of the different networks with the corresponding mappings to the Open Systems Interconnection (OSI) reference model.

Figure 3. CIP common layering over different networks

DeviceNet [24] was the first member of this protocol family and it is a CIP implementation of the Controller Area Network (CAN) protocol layer. In its typical form, (ISO 11898, [26]) CAN only defines the Data Link Layer (DLL) and Physical Layer of the 7-layer OSI reference model, while DeviceNet covers the upper layers. The low cost of implementation and the ease of use of DeviceNet has led to a considerable popularity, nevertheless, it is limited to the small payload of the CAN protocol (8 bytes) and to the maximum 1 Mbps bandwidth obtainable with CAN.

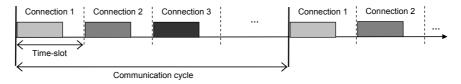

ControlNet [25], introduced in 1997, essentially implemented the same protocol on a new physical layer, based on a specific method called Concurrent Time Domain Multiple Access (CTDMA). Weighed against CAN, CTDMA allows a higher throughput (5 Mbps), induces strict determinism and repeatability, while extending the length of the bus. ControlNet comes, however, with a fairly high price tag, being its usage restricted to the more demanding applications.

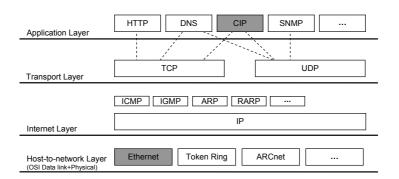

EIP was the latest addition to the CIP family. It is based on Ethernet and implements the CIP distributed object model using TCP/UDP/IP services. Figure 4 presents the relation of CIP to other protocols in a TCP/IP conceptual model.

Figure 4. CIP and Ethernet in the TCP/IP layering model

### 2.3.2 CIP Messaging

In CIP-based networks the majority of the messaging performed is done through connections. *CIP connections* define the packets that will be produced on the network, and these can be of two types: *Explicit* or *Implicit messaging*.

Explicit messaging connections provide generic, multipurpose communication paths between two devices. Explicit messages provide the typical request/response-oriented network communication. Each request contains explicit information that the receiving node decodes, acts upon, and to which generates an appropriate response.

Implicit messaging connections provide dedicated, special purpose communication paths between a producing application object and one ore more consuming application objects. They are called implicit messages because the data that will be exchanged is identified at the time the connection is established and connection identifiers are assigned. Then, each transmission contains only the current values for the application objects that where agreed upon when the connection was established and the connection identifier, thus having a very small overhead.

There are four principal types of Implicit messages: *Polled, Strobed, Cyclic and Change of State (CoS)*. With polled messages, a device assumes the role of master and sequentially queries all of the slave devices by sending their output data and allowing them to reply with their input data. Strobed is a special case of polled in which the master sends out a single multicast request for data and the slaves sequentially reply with their data, requiring no further messages from the master. Cyclic messages are produced on a predetermined rate basis, defined by the *Requested Packet Interval* (RPI) parameter. In Change of State, as the name suggests, messages are only produced in response to an event which caused the data to change. Change of State also maintains a background cyclic rate so that consuming applications know that the node is still online.

Implicit messaging is the messaging used for time critical I/O data, and therefore will receive the focus of our attention, specially the Cyclic Implicit CIP connections.

### 2.3.3 Producer/Distributor/Consumer Model

As mentioned in the previous section, underlying CIP messaging is a *producer/distributor/consumer* model, replacing the more conventional *source/destination* (master/slave) model. The producer/distributor/consumer model is also usually found in other factory communication networks [27].

In a source/destination model (Figure 5), the source communicates with each destination, one at a time. Real-time data must be adjusted to maintain accuracy as communication takes place with each source, one at a time. Some of the destinations may not need the information, so there is some bandwidth waste. Moreover, the delivery time changes with the number of destination devices.

Figure 5. Source/destination model illustration

In the producer/distributor/consumer model (Figure 6) one producer broadcasts (multicasts) the data once to all the consumers. All consumers see the data simultaneously, and may choose whether to consume (receive) the data or not. Delivery time is consistent and bandwidth usage is optimised, no matter how many consumers exist.

Figure 6. Producer/distributor/consumer model illustration

In EIP networks, the distribution of messages is supported upon multicast UDP/IP that, in turn, is mapped onto Ethernet multicast.

In multicast UDP/IP, packets are not transmitted directly to the IP address of the destination node. Instead, they are transmitted to a specific address that identifies a group of nodes – an IP multicast address. Nodes may joint/leave groups using Internet Group Management Protocol (IGMP) messages. Generally, nodes will join multicast groups at connection establishment time, using information exchanged during this process.

The advantages of using multicast UDP/IP are twofold: firstly, it is the lightest transport layer, introducing the least amount of overhead for processing and transmitting each

message; secondly, multicast-based transmission facilitates the distribution of data to multiple destinations.

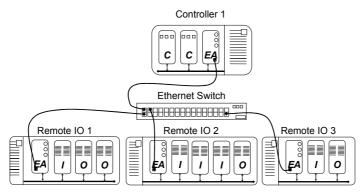

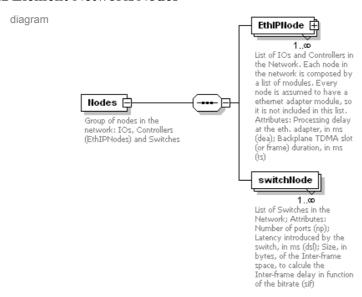

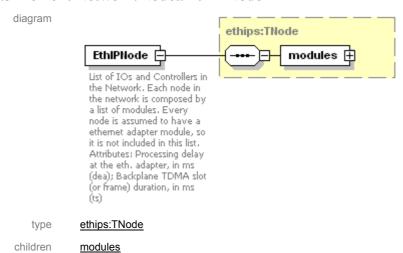

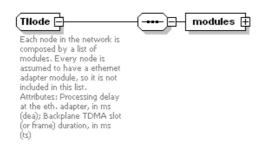

### 2.3.4 Ethernet/IP Devices

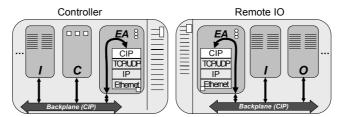

EIP networks are constituted by three structuring types of nodes: *Remote I/Os, Controllers* and interconnecting *Switches*. Diverse modules can compose the Remote I/O and Controller nodes (Figure 7). Typically, a Controller is composed of a number of *I/O modules* (labelled in the Figure 7 as I or O), several *Controller modules* (C) and one or more *Ethernet Adapters* (EA). A Remote I/O node has no Controller modules.

Figure 7. EIP basic nodes

Within each node, the several modules communicate among them via a device-specific backplane. The nodes communicate with each other via Switched Ethernet. Inside the node, communication is based on CIP messages and, when the messages are to be delivered to another node, these messages are encapsulated in TCP/UDP/IP packets by the Ethernet Adapter.

In the case of time critical data, as referred earlier, these messages are encapsulated in UDP/IP packets and delivered using multicast services. The periodicity of time critical data CIP connections is maintained internally in each producing module. Each module maintains a timer for the configured RPI of each connection.

In the following section, the diverse components of the end-to-end latency are introduced, leading to a first delineation of the end-to-end delay in EIP to be analysed. It is important to stress the fact that some of the architectural details and implementations are open to alternative options from technology providers. The descriptions presented are a result of information gathered from a technology provider, and of assumptions taken from the available information. The general assumptions made on the devices and network analysis are also within the next section.

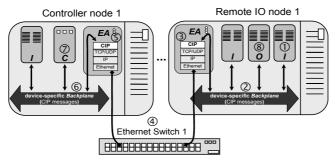

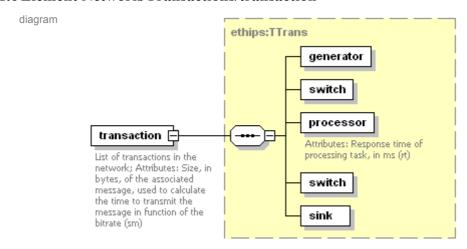

### 2.3.5 Defining an End-to-End Transaction

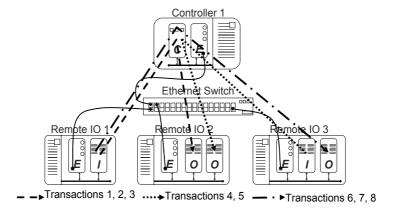

The several components considered to makeup an end-to-end EIP transaction are illustrated using the following simple EIP network (Figure 8).

Figure 8. EIP end-to-end transaction

The EIP transaction considered is an independent transaction, starting at the input module of the Remote I/O (①). After the hardware delay to energise the input and a user defined filter delay, a message with the input data will be generated, at the periodicity defined for the input data connection. This message will then suffer the contention caused by the device backplane (②), and will arrive at the Ethernet Adapter, where it is processed, encapsulated and transmitted via the Ethernet communication interface (③). With this, the message arrives at the Ethernet switch, where it is relayed to the corresponding output port(s), and later will arrive at the Controller Ethernet Adapter (④). At the Ethernet Adapter (⑤), the message is processed, in order to be passed to the Controller module, passing through the Controller backplane (⑥). At the controller the input data will be processed by a controller task, characterised by a worst-case response time, that generates the corresponding output data (⑦). The output data will be transmitted at a defined periodicity and will go back through the inverse path (⑥,⑤,④), until it reaches the Ethernet Adapter of the Remote I/O (③), is processed and delivered to the output module that will, in result, energise the corresponding output(s) (⑧).

### 2.3.6 Assumptions

Before continuing, a few words on assumptions are worthy to be provided. Throughout the development of the EIP models to be later described in this dissertation, a number of assumptions where introduced in order to narrow, in some reasonable way, the number of variables needed to be accounted for. Additionally, these assumptions also reflect some of the implementation details specific of the considered EIP devices.

Thus, the following assumptions will be considered:

- traffic in the network is restricted and isolated;

- processing and network traffic related to the network setup period is negligible;

- only Cyclic Implicit CIP connections are assumed to exist in the network, and their periods are known;

- the controller tasks are independent, execute periodically and have a bounded worst-case response time;

- during task execution, the input data is processed and corresponding output data is generated once;

- packet processing time in the Ethernet Adapter is characterised;

- time to transfer a frame in the Backplane is characterised;

- the input filter delay is a known variable, defined by the user;

- output module hardware delay is negligible;

- network data rate is known;

- switch latency and other switch processing delays are characterised;

- propagation delays are ignored.

### 2.4 Summary

Characteristics like generous bandwidths, switching technologies, priority handling and support for widely spread upper protocol stacks are driving an increasing eagerness for extending Ethernet to also cover factory-floor distributed real-time applications. This chapter exposed the basics of Ethernet technology and the developments of factory-floor communication systems driving that eagerness.

Additionally, the Commercial-Off-The-Shelf (COTS) factory-floor communication system to be investigated – Ethernet/IP (EIP) – is introduced in this chapter. The fundamentals of CIP, the application layer protocol used by EIP, were brought out, and some details of the EIP devices considered for the analysis were conveyed. Finally, the assumptions included in the analysis to be presented later in this dissertation were enumerated.

### Chapter 3

## TECHNOLOGICAL CONTEXT: SIMULATION SOFTWARE

### 3.1 Introduction

Simulation is basically the imitation of the operation of a real-world system over time. The availability of special-purpose simulation languages, increasing computing capabilities at a decreasing cost per operation and advances in simulation methodologies, have made simulation one of the most accepted tools in operations research and systems analysis [28].

Simulation, for the study of any system, usually involves the development of a model, where the details and behaviour that affect the system under study are represented. A model of a system can be classified, according to its nature and system modelled, into several different types. Simulation models can be classified as being *static* or *dynamic*, *deterministic* or *stochastic*, and *discrete* or *continuous*. A static simulation model represents a system at a particular point in time, while dynamic simulation models represent systems as they change over time.

Simulation models that contain no random variables are classified as deterministic. Deterministic models have a known set of inputs, which will result in a unique set of outputs. On the other hand, a stochastic model has one or more random variables as inputs, which result in random outputs.

A system can be classified as discrete or continuous, according to the way its state variables change. The state of a system is defined to be the collection of variables necessary to describe the system at any time, relative to the objectives of the study. When the state variables change only at a discrete set of points in time, the system is classified as discrete. Conversely, in a continuous system, the state variables change continuously over time. In practice, very few systems are strictly discrete or strictly continuous, but since one type predominates for most systems, it is usually acceptable to classify a system as either being discrete or continuous [28].

In the case of discrete-event simulation, the model is analysed by numerical rather than by analytical methods. Analytical methods employ the deductive reasoning of mathematics to *solve* the model. Numerical methods employ computational procedures to *solve* analytical models. In the case of simulation models, which employ numerical methods, models are *executed* rather than *solved*. That is, an artificial history of the system is generated based on the model assumptions, and observations are collected to be analysed and to estimate the true system performance measures.

Predominantly, computer systems and communication networks are described by state variables that change discretely, justifying the choice for developing discrete-event simulation models.

The considerable amount of established techniques for its development and analysis and the large number of software packages readily available for this type of simulation, are just some of the additional characteristics that further corroborate this option. Some simulation tools will be overviewed throughout this chapter.

Generally, the implementation of discrete-event simulation models encompasses a number of common features such as:

- generation of random numbers;

- advancing simulated time;

- maintaining a list of events;

- determining the next event from the list;

- passing control to the appropriate block of code;

- collecting output data;

- detecting error conditions.

These features are, in reality, so common in the implementation of discrete-event simulation models that they have led to the emergence of special-purpose simulation software tools that provide these common facilities for the implementation of simulation models. These software tools can be generally classified in two distinct categories: simulation languages and simulation packages. The latter can be divided in application-oriented and general-purpose simulation packages.

A deeper debate of this matter shall not be attended. As this dissertation is focusing on the simulation of a communication network, a discussion of application-oriented simulation packages for this purpose will suffice.

### 3.2 Simulation Languages

Simulation languages provide maximum flexibility for the simulation developer who wants to construct simulators by means of programming. Because most simulation languages have expressive power equivalent to a general-purpose programming language, the simulation developer has great flexibility in designing and implementing the simulator. The trade-off for this flexibility is the development effort required to program the simulator.

Much work has been done at the simulation language level, either in the form of true languages or as function libraries. Some examples of freely available simulation languages in use today are briefly addressed below.

PARSEC (PARallel Simulation Environment for Complex systems) [29] is a C-based simulation language developed by the Parallel Computing Laboratory from the University

of California, Los Angeles, for sequential and parallel execution of discrete-event simulation models. It is available in binary form only for academic institutions.

SMURPH (System for Modelling Unslotted Real-time PHenomena) [30] is intended for simulating communication protocols at the medium access control (MAC) level. SMURPH can be viewed as a combination of a protocol specification language based on C++ and an event-driven, discrete-time simulator that provides a virtual and controlled environment for protocol execution. SMURPH can be used for designing low-level communication protocols and for investigating their quantitative and qualitative properties.

SIMSCRIPT [31] is a simulation language with both declarative and procedural features, designed for discrete-event and hybrid discrete/continuous modelling. It has been in continuous use and development since its invention in 1962. The syntax and semantics of SIMSCRIPT II are designed to make simulation programs easy to write and understand. The language syntax is "English-like" and fairly high-level. Today, SIMSCRIPT II.5 is more than a simulation language, being a commercial product offered by CACI Products Company. An important contribution from SIMSCRIPT is its considerable impact on the development of SIMULA (SIMUlation LAnguage), through its list processing, time scheduling mechanisms, random drawing and other utility routines.

The SIMULA [32] programming language was designed and built at the Norwegian Computing Centre (NCC) in Oslo between 1962 and 1967. It was originally designed and implemented as a language for discrete event simulation, but was later expended and reimplemented as a full scale general purpose programming language. Although SIMULA never became widely used, the language has been highly influential on modern programming methodology.

CSIM/C++SIM [33] is a programming tool for simulation of discrete processes. It is an extension of the C language obtained by including SIMULA-like possibilities by means of C macros and functions. CSim uses a special C-functions and C-macros library. The typical application area of CSim is functional validation of distributed, parallel and fault-tolerant systems and programs. Similarly, C++SIM is a collection of C++ libraries.

### 3.3 Network Simulation Packages

Network simulation packages provide a more comprehensive support than simulation languages. They include the basic constructs for the development of network simulation, typically require less programming effort and have a smoother learning curve, when compared to simulation languages. Many network simulation packages include some type of pre-built and reusable models of networking protocols, devices and applications. Additionally, they also provide means for using and creating user interfaces to the simulation models, facilitating their development, debugging and understanding.

There exist several examples of such simulation packages. Some characterisation to a number of these is provided next.

OPNET [34] is widely held as the state-of-art in network simulation. It is a suite of products that combines predictive modelling and a comprehensive understanding of networking technologies to enable design, deployment, and management of network infrastructures, network equipments, and networked applications. In particular, OPNET

Modeller is a development environment, allowing to design and study communication networks, devices, protocols, and applications. OPNET is a commercial product, although it provides some academic licensing programmes, albeit with some restrictions.

NetSim [35] is intended to offer a very detailed simulation of Ethernet, including realistic modelling of signal propagation, the effect of the relative positions of stations on events on the network, the collision detection and handling process and the transmission deferral mechanism. However, its development has stagnated and it is infeasible its extension in order to address modern networks.

CNET [36] is a discrete-event network simulator enabling experimentation with various data-link layer, network layer, routing and transport layer networking protocols. It has been specifically developed for, and used in, undergraduate computer networking courses taken by thousands of students worldwide.

Ns-2 (Network Simulator 2) [37] is a discrete event simulator targeted at networking research. Ns-2 provides substantial support for simulation of TCP, routing, and multicast protocols over wired and wireless (local and satellite) networks. Ns began as a variant of the REAL [38] network simulator in 1989, and has evolved substantially over the past few years. The full source code of ns-2 can be downloaded and it can be compiled in multiple platforms, including the most popular UNIX flavours and Windows.

OMNeT++ (Objective Modular Network Testbed in C++) [39], is a public-source, object-oriented modular discrete event simulation package that can be used for modelling communication protocols, computer networks, traffic modelling, multiprocessors and distributed systems. OMNeT++ also supports animation and interactive execution.

The previous list is not, by any means, comprehensive. It presents the several options considered for the development of the work presented in this dissertation. Among the simulation packages described, only ns-2 and OMNeT++ were assessed has possible solutions for the use in the work described by this dissertation. While ns-2 is a network simulation classic, it has many drawbacks, when compared with OMNeT++, which is a more modern and structured simulation package. The following summarises a number of advantages from OMNeT++ over ns-2.

- the OMNeT++ simulation kernel is a class library: the components are developed as any other class library, and then linked with the executable library. There is no need to modify OMNeT++ sources anywhere. In contrast, ns-2 tends to be a bit monolithic: to add implementations to it, it is necessary to download the full source and modify it in several places;

- OMNeT++ follows a modular approach: the model is assembled from selfcontained building blocks. These components are reusable "as is" in other simulations:

- ns-2 has some considerably detailed built-in concepts about nodes, agents, protocols, links, packet representation, network addresses, etc. This often increases the difficulty in developing models that include even slightly different concepts. OMNeT++ is completely flexible and generic: it is possible to simulate anything that can be mapped to active components that communicate by passing messages;

- in OMNeT++, it is possible to fight model complexity by using hierarchical design: any complex component can be implemented as one unit or built out of several smaller components. In ns-2, models are "flat":

- OMNeT++ has a powerful interactive graphical environment, where it is possible to examine nearly everything during execution. Ns-2 only includes Network AniMator (NAM), which is little more than a playback tool.

### 3.4 A Few More Details on OMNeT++

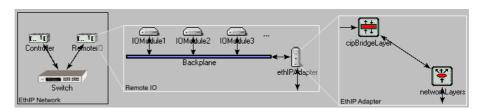

OMNeT++ is a discrete event simulation package written in C++ with a primary application area in the simulation of computer networks and other distributed systems. The OMNeT++ simulation models are composed of hierarchically nested modules that communicate with message passing. Modules at the lowest level are programmed using C++, while the model structure is defined by a topology description language. Using this topology description language, modules can be combined and reused flexibly.

The package contains the C++ simulation kernel library, a manual, a simulation kernel API reference, a graphical topology editor, a graphical runtime environment with interesting animation and tracing capabilities, as well as a command-line runtime environment for batch execution. It also includes several other tools and sample simulations.

One of the strengths of OMNeT++ is that one can execute the simulation under a graphical user interface with interesting features. The GUI makes the internals of a simulation model fully visible to the person running the simulation: it displays the network graphics, animates the message flow and lets the user peek into objects and variables within the model. The use of the tracing/debugging capabilities does not require extra code to be written by the simulation programmer.

OMNeT++ already contains detailed IP, TCP, and FDDI protocol models and several other simulation models (file system simulator, Ethernet, a framework for simulation of mobility, etc.). However, the simulation model suite for OMNeT++ has not crystallised yet and many of these models are still under development.

OMNeT++ is open source, free for non-profit usage, and has an active user community. It has been tested on Linux, Solaris, Windows and Mac OSX. The Web site [40] provides source code, binaries, documentation, mailing lists, a Web-based discussion forum and information on workshops. OMNeT++ modelling concepts will be briefly described now.

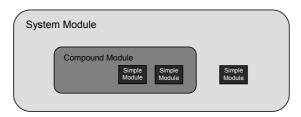

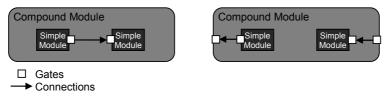

An OMNeT++ model is composed of hierarchically nested modules which communicate with messages. The top level module is the *system module* (often called *network*). The system module contains *sub-modules*. These sub-modules may be of two different types: *compound modules* and *simple modules*. Modules that can contain sub-modules are termed compound modules. These may contain an unlimited nesting of sub-modules. Conversely, modules that do not contain any sub-modules are called simple modules and are at the lowest level of the module hierarchy (Figure 9).

Figure 9. OMNeT++ module hierarchy

Simple OMNeT++ modules contain the algorithms of the models. These are implemented as C++ classes derived from a simple module base class, by redefining the virtual function that contains the algorithm. The full flexibility and power of the programming language can be used, supported by the OMNeT++ simulation class library.

Modules communicate by exchanging messages. In a simulation, messages can represent frames or packets in a communication network, jobs or customers in a queuing network, or other types of mobiles entities. OMNeT++ class library includes a message base class. This class can be extended to arbitrarily represent any type of mobile entity needed for the simulation model.

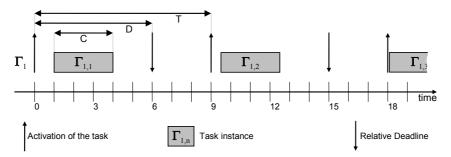

Simple modules can send messages either directly to their destination or along a predefined path, through *gates* and *connections*. Gates are the input and output interfaces of modules. Messages are sent out to *output gates* and received through *input gates*. Each connection is created within a single level of the module hierarchy. In a compound module one can connect the corresponding gates of two sub-modules, or a gate of one sub-module and a gate of the compound module (Figure 10). Due to the hierarchical structure of the model, messages typically travel through a series of connections, to start and arrive in simple modules.

Figure 10. OMNeT++ gates and connections

To help modelling transmission channels and packet transmissions, connections can be assigned three parameters: *propagation delay*, *bit error rate* and *data rate*. All these three are optional. One may specify link parameters individually for each connection, or define link types and use them throughout the whole model. For example, by defining the data rate of a connection, it is possible to model the transmission time of a packet by using the size attribute from the message class that represents the packet.

The structure of the modules (both simple and compound) is defined using NEtwork Description (NED). The NED language supports the definition of the network's topology in a modular fashion. A network description consists of a number of component descriptions (channels, simple/compound module types). The channels, simple modules and compound

modules of one network description can be reused in another network description. As a consequence, the NED language allows users to build their own module libraries.

All modules can have parameters that can be used to parameterise the module topology, customise simple module behaviour, or for module communication. Parameters can be numeric values, expressions using other parameters, calling of C functions, random variables from different distributions, and values input interactively by the user.

## 3.5 Summary

Simulation may present itself as an appealing option for analysing the timing properties of EIP-based distributed systems. This chapter introduced some basic concepts and options on simulation software. The progress of the chapter sustained the choice for the OMNeT++ simulation package, to which some further details were provided.

# Chapter 4

### APPROACHES FOR TIMELINESS ANALYSIS

### 4.1 Introduction

In this chapter, basic concepts of real-time systems are laid out to introduce the foundations of traditional real-time response time analysis, some of which may also be applicable to the analysis of distributed systems. The next two sections addresses concepts firstly associated with single processor systems, which are then adapted and extended to be applied in the analysis of distributed systems.

In this chapter some aspects related to the application of simulation-based approaches to perform timeliness analysis will be also covered. An essential component of a simulation-based analysis is the development of accurate simulation models and the adequate exploration of the produced output data. In section 4.4, both of these issues are addressed.

# 4.2 Basic Concepts of Real-time Systems

Real-time computing systems are defined as those systems in which the correctness of the system depends not only on the logical result of computation, but also on the time at which the results are produced [41]. There are various examples of real-time computing systems, such as command and control systems, flight control systems or robotics.

A typical real-time computing system has a real-time program running on the system, which reads inputs from input devices, processes these inputs, and often produces outputs to be sent to output devices. The time between the arrival of an input from a device and the completion of the processing for that input is called the *response time* for the device [42]. The *relative deadline* for the device can be defined as the maximum admissible interval between the instant of the input arrival and the completion of the processing for that input. Hence, the response time for a device must be smaller or equal to its relative deadline.

Assume that each input device is assigned a task (process) of the application program and that the tasks share a same processor. The problem of determining whether the system will meet its peak processing load, or in other words, whether no input from any device will be lost, becomes one of schedulability analysis of tasks [43].

A round-robin scheduling policy ensures that each task gets a share of the processor. However, such an approach may not be suitable for real-time systems. Assume the following example [44]: "Consider a computer controlling an aircraft. Among its tasks are maintaining stability and keeping the cabin temperature within acceptable limits. Suppose the aircraft encounters turbulence that makes it momentarily unstable. The computer is then supposed to adjust the control surfaces to regain stability. If we use round-robin scheduling

for this application, the computer may switch context partway through making the control adjustments in order to spend time making sure the cabin temperature is just right. The result may well be a crash, and the fact that the cabin is being maintained at optimum temperature will be scant consolation to the passengers as the airliner falls out the sky. What we want is to give the stability-maintenance task a very high priority, which ensures that when stability is threatened, all other interfering tasks are elbowed out of the way to allow this all-important task enough computer cycles."

It follows that the consideration of priority levels is crucial to a real-time computing system. If different inputs have different response time requirements, we need to consider different *priority levels* to *schedule* the related processing tasks. Consider a real-time system, within which several devices are connected at different priority levels to a single processor computer system. An input being processed will be preempted when another input of higher priority arrives, and will only be resumed when there is no processing remaining at higher priorities.

Assume that the input from a device is saved in a buffer, until it is overwritten by the next input of the same device. The problem is to determine whether for a given assignment of priority levels, the system will meet its peak processing load (i.e. no input from any device will be lost). A more basic problem is how to assign devices to priorities in order to meet the system-processing load.

#### 4.2.1 Characterisation of Tasks

There is a number of attributes related to a task in a real-time system, typically including the following:

- *C*, the worst-case execution time (WCET) of the task;

- T, for periodic tasks it is the minimum time between arrivals of instances of the same task;

- D, the relative deadline of the task, i.e., the maximum time allowed between the release of the task and completion of its execution;

- P, priority level assigned to the task;

- B, longest time a task may be blocked by a lower priority task;

- R, worst-case response time of a task (most schedulability analyses try to verify if R < D).</li>

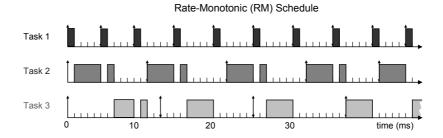

To illustrate these attributes, consider a task ( $\Gamma_l$ ) that is released periodically (every 9 time units) to perform some kind of processing. The worst-case execution time (C) of the task is 3 time units, and its relative deadline (D) is 6. Several instances ( $\Gamma_{l,l}$ ,  $\Gamma_{l,2}$ ,...,  $\Gamma_{l,n}$ ) of task  $\Gamma_l$  are depicted in Figure 11.

Figure 11. Illustration of task attributes

Tasks can also be characterised according to their predictability. This characteristic of the tasks affects their schedulability analysis. Concerning the predictability, three basic types of tasks can be defined: *periodic*, *aperiodic* and *sporadic*.

Periodic tasks, as their name implies, are released on a regular basis. They are characterised by their period, their deadline and their required execution time per period. The deadline is often assumed to be equal to the period, i.e. the processing of an input must be completed, at most, before the next input from the same device.

Aperiodic tasks are released only occasionally, and are usually triggered by an external event. To allow worst-case calculations to be made, a minimum period between any two aperiodic inputs (from the same device) is often defined. If this is the case, the task involved is said to be sporadic, and its period corresponds to its minimum inter-arrival time.

Tasks can also be characterised according to their criticality, depending on the consequences of not being executed before their deadlines. Concerning their criticality real-time tasks can be *soft*, *hard* or *safety-critical*.